# UNLEASH THE POWER OF AVX-512 THROUGH ARCHITECTURE, COMPILER AND CODE MODERNIZATION

Xinmin Tian, Robert Geva, and Bob Valentine Intel Corporation September 11, 2016

PACT 2016 Tutorial, Haifa, Israel

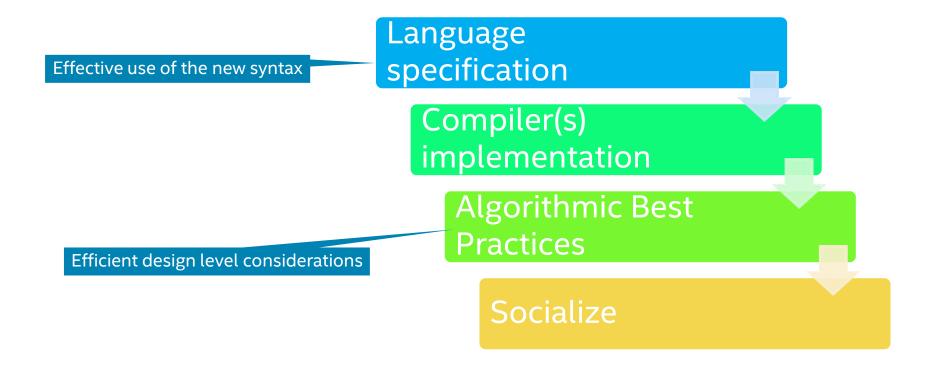

# Agenda

Section I - AVX-512 Architecture Insights Section II - Intel<sup>®</sup> Compiler: Putting SIMD Vectorization to Work Section III - Code Modernization: Best Practices for Vector Programming

# **AVX512 ARCHITECTURE INSIGHTS**

Robert Valentine – Senior Principal Engineer Intel Corporation September 11, 2016

PACT 2016 Tutorial, Haifa, Israel

# Section I: Agenda

- ✓ Introduction: Intel<sup>®</sup> ISA Roadmap

- ✓ Deep dive: AVX1/2/AVX512 ISA

- ✓ AVX-512 F: Common ISA Extension

- ✓ AVX-512 ERI & PRI: Intel® Xeon Phi<sup>™</sup> Product Only

- ✓ Xeon additions to AVX-512 F

- ✓ Summary

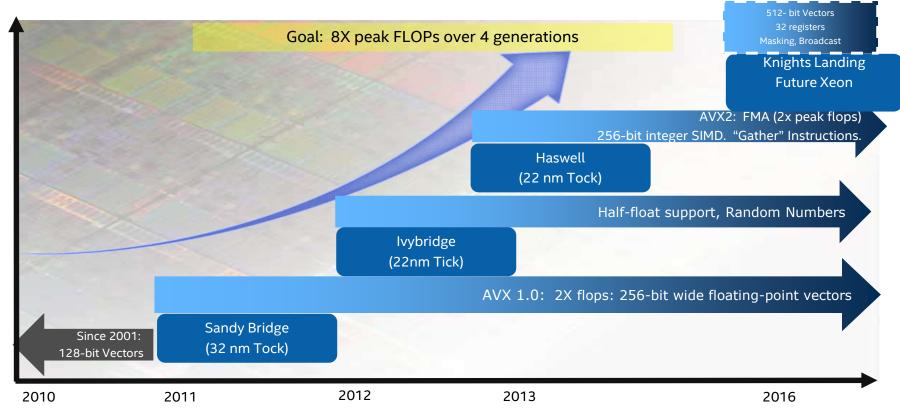

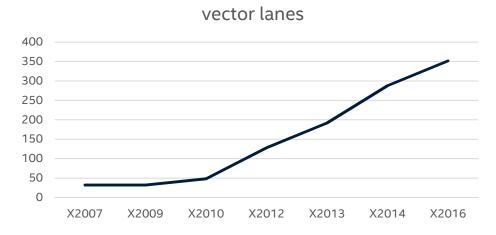

#### Intel<sup>®</sup> Advanced Vector Extensions

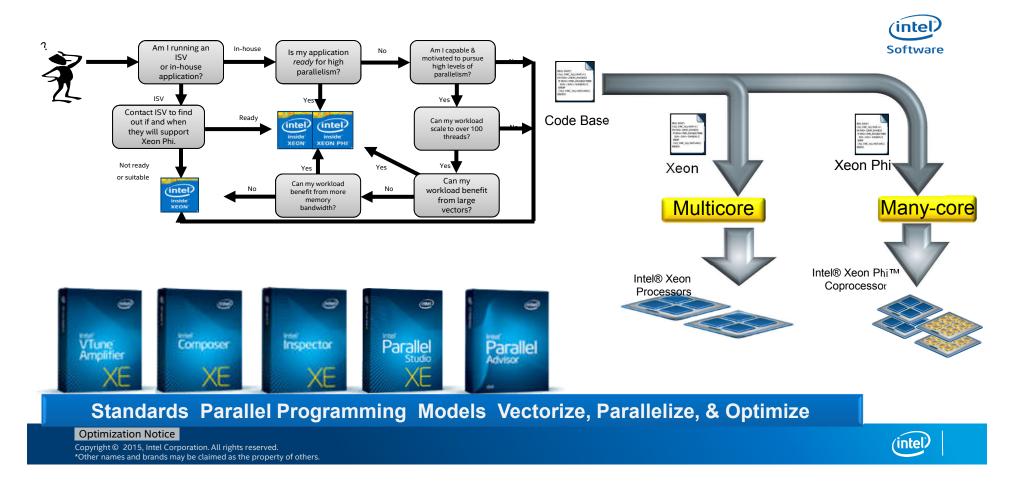

#### **Consistent Developer Tools and Programming Models**

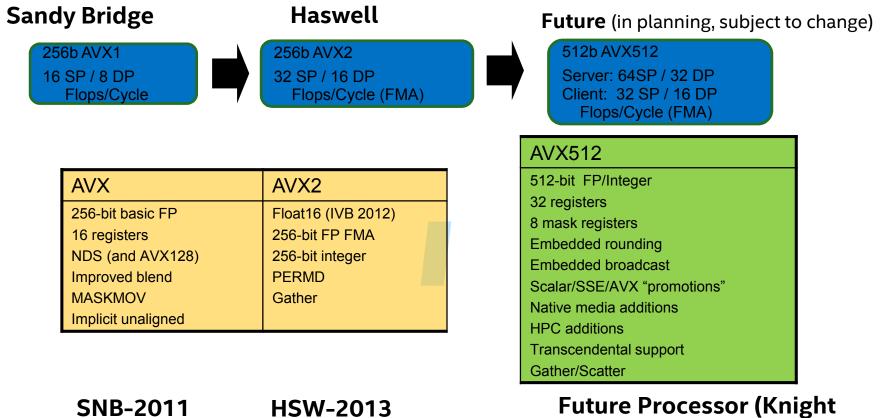

## Intel<sup>®</sup> AVX Technology

Landing & future Xeon)

# **AVX512 Big Picture**

- ✓ Deep dive: AVX1/2/AVX512 ISA

- ✓ AVX-512 F: Common ISA Extension

- ✓ AVX-512 ERI & PRI: Intel<sup>®</sup> Xeon Phi<sup>™</sup> Product Only

- ✓ Xeon additions to AVX-512 F

### AVX512 big picture

#### AVX512F

- 'Foundation' of architecture, required for any AVX512 implementation

- Many D/Q/SP/DP promotions from AVX2 with AAVX512 features

- Masking, 32 registers, embedded broadcast or rounding, 512-bit Vector Length

- New instructions added to accelerate HPC workloads

- Implementations add features to AVX512F "base"

- "base" will grow as MIC/Xeon converge on features

| AVX512C | D Conflict Detect : instructions tailored for vectorizing loops with potential address conflicts |

|---------|--------------------------------------------------------------------------------------------------|

| AVX512E | R Exponential and Reciprocal : 'wide' approximateion of Log (22 bits) and RCP/RSQRT (28 bits)    |

| AVX512P | F Prefetch : Multi-address prefetch instructions using gather/scatter semantics                  |

|         |                                                                                                  |

| AVX512D | Q Additional D/Q/SP/DP instructions (converts, transcendental support, etc)                      |

| AVX512B | W 512-bit Byte/Word support (promotions from AVX2, some additions)                               |

| AVX512V | L Vector Length Orthogonality : ability to operate on sub-512 vector sizes                       |

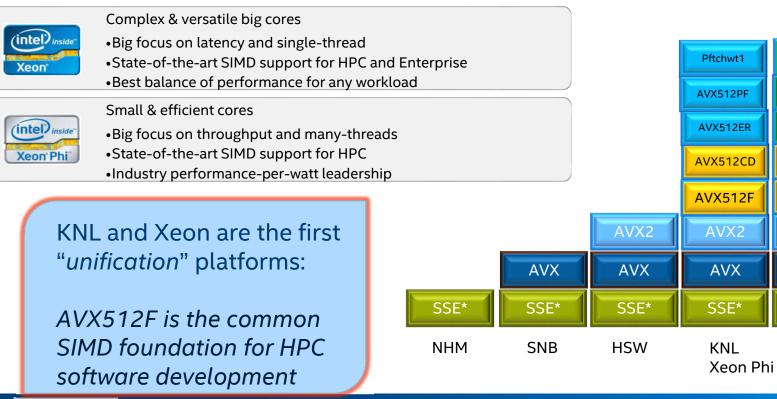

### Xeon & Xeon Phi<sup>™</sup> New ISA: What Is Where?

Optimization Notice Copyright © 2015, Intel Corporation. All rights reserved. <u>\*Other names and brands may be claimed as the property of others.</u>

AVX512VL

AVX512BW

AVX512DQ

AVX512CD

AVX512F

AVX2

AVX

SSE\*

Future

Xeon

### AVX-512 features (I): More & Bigger Registers

#### AVX: VADDPS YMM0, YMM3, [mem]

- Up to 16 AVX registers

- 8 in 32-bit mode

- 256-bit width

- 8 x FP32

- 4 x FP64

#### AVX-512: VADDPS ZMM0, ZMM24, [mem]

- Up to 32 AVX registers

- 8 in 32-bit mode

- 512-bit width

- 16 x FP32

- 8 x FP64

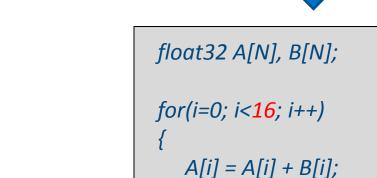

float32 A[N], B[N];

A[i] = A[i] + B[i];

(intel)

for(i=0; i<8; i++)

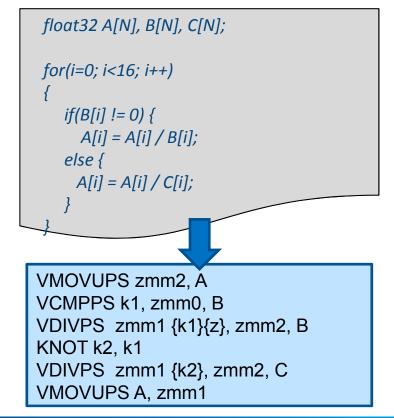

### **AVX-512 Mask Registers**

#### 8 Mask registers of size 64-bits

- k1-k7 can be used for predication

- k0 can be used as a destination or source for mask manipulation operations

#### 4 different mask granularities. For instance, at 512b:

- Packed Integer Byte use mask bits [63:0]

- VPADDB zmm1 {k1}, zmm2, zmm3

- Packed Integer Word use mask bits [31:0]

- VPADDW zmm1 {k1}, zmm2, zmm3

- Packed IEEE FP32 and Integer Dword use mask bits [15:0]

- VADDPS zmm1 {k1}, zmm2, zmm3

- Packed IEEE FP64 and Integer Qword use mask bits [7:0]

- VADDPD zmm1 {k1}, zmm2, zmm3

|       | VAD   | OPD : | zmm1  | {k1]  | } <u>,</u> zr | nm2,  | zmm <sup>3</sup> | 3  |  |

|-------|-------|-------|-------|-------|---------------|-------|------------------|----|--|

| zmm1  | a7    | a6    | a5    | a4    | a3            | a2    | a1               | a0 |  |

| zmm2  | b7    | b6    | b5    | b4    | b3            | b2    | b1               | b0 |  |

| 20002 |       |       |       |       |               |       |                  |    |  |

| zmm3  | c7    | c6    | c5    | c4    | c3            | c2    | c1               | c0 |  |

|       | Ð     | Ð     | Ð     | Ð     | Ð             | Ð     | Ð                | Ð  |  |

| k1    |       |       |       |       |               |       |                  |    |  |

| zmm1  | b7+c7 | a6    | b5+c5 | b4+c4 | b3+c3         | b2+c2 | a1               | aO |  |

|         |           | Vector Length |     |     |  |  |

|---------|-----------|---------------|-----|-----|--|--|

|         |           | 128           | 256 | 512 |  |  |

|         | Byte      | 16            | 32  | 64  |  |  |

| Word    |           | 8             | 16  | 32  |  |  |

| element | Dw ord/SP | 4             | 8   | 16  |  |  |

| size    | Qw ord/DP | 2             | 4   | 8   |  |  |

### AVX-512 Features (II): Masking

#### VADDPS ZMM0 {k1}, ZMM3, [mem]

- Mask bits used to:

- 1. Suppress individual elements read from memory

- hence not signaling any memory fault

- 2. Avoid actual independent operations within an instruction happening

- and hence not signaling any FP fault

- 3. Avoid the individual destination elements being updated,

- or alternatively, force them to zero (zeroing)

```

for (I in vector length)

{

if (no_masking or mask[I]) {

dest[I] = OP(src2, src3)

} else {

if (zeroing_masking)

dest[I] = 0

else

// dest[I] is preserved

}

}

```

Caveat: vector shuffles do not suppress memory fault exceptions mask refers to "output" not to "input"

### Why True Masking?

#### Memory fault suppression

- Vectorize code without touching memory that the correspondent scalar code would not touch

- Typical examples are if-conditional statements or loop remainders

- AVX is forced to use VMASKMOV\* (risc)

#### MXCSR flag updates and fault handlers

Avoid spurious floating-point exceptions without having to inject neutral data

#### Zeroing/merging

- Use zeroing to avoid false dependencies in OOO architecture

- Use merging to avoid extra blends in if-then-else clauses (predication) for great code density

Optimization Notice Copyright © 2015, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others

(intel)

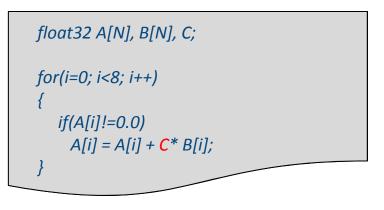

### **Embedded Broadcasts and Masking Support**

#### VFMADD231PS zmm1, zmm2, C {1to16}

- Scalars from memory are first class citizens

- Broadcast one scalar from memory into all vector elements before operation

- Memory fault suppression avoids fetching the scalar if no mask bit is set to 1

#### Other "tuples" supported

- Memory only touched if at least one consumer lane needs the data

- For instance, when broadcast a tuple of 4 elements, the semantics check for every element being really used

- E.g.: element 1 checks for mask bits 1, 5, 9, 13, ...

VBROADCASTSS zmm1 {k1}, [rax] VBROADCASTF64X2 zmm2 {k1}, [rax] VBROADCASTF32X4 zmm3 {k1}, [rax] VBROADCASTF32X8 zmm4, {k1}, [rax]

. . .

#### AVX-512 Features: Embedded Rounding Control & SAE (Suppress All Exceptions)

- MXCSR.RC can be overridden on a per instruction basis (Embedded Rounding Control )

- VADDPS ZMM1 {k1}, ZMM2, ZMM3 {rne-sae}

- VADDSS XMM1 {k1}, XMM2, XMM3 {rrtz-sae}

- "Suspend All Exceptions" (always implied by using Embedded Rounding Control)

NO MXCSR updates / exception reporting for any element

Restricted to : FP instructions 512-bit or scalar Reg-reg operands

#### Expected usage of this feature

- Library codes can control effect of rounding and updates to MXCSR until the end stages of complex SW routines

- E.g.: avoid spurious overflow/underflow reporting in intermediate computations

- E.g: make sure that RM=rne regardless of the contents of MXCSR

- Saving, modifying and restoring MXCSR is generally slower and more and cumbersome

- Must use LDMXCSR to change fault masks, clear sticky bits or set a default rounding mode

- Do not need to use MXCSR OR embedded rounding for truncating FP conversion to int (use CVTT\* instructions)

#### AVX-512 F: Common Xeon Phi (KNL) and Xeon Vector ISA Extension

AVX-512 Foundation is the common SIMD foundation for HPC software development First on KNL Planned on a future Xeon

### **AVX-512 F Designed for HPC**

Promotions of many AVX and AVX2 instructions to AVX-512

32 bit and 64 bit floating point instructions from AVX

32-bit and 64-bit floating-point instructions from AVX

Scalar and 512-bit

32-bit and 64-bit integer instructions from AVX2

Many new instructions to speedup HPC workloads

### **Quadword Integer Arithmetic**

Long int and packed pointer manipulation 64-bit integer trending towards becoming a first class citizen Removes the need for expensive SW emulation sequences

Note: VPMULQ and int64 <-> FP converts not in AVX-512 F

| Instruction                                        | Description                 |

|----------------------------------------------------|-----------------------------|

| <pre>VPADDQ zmm1 {k1}, zmm2, zmm3</pre>            | INT64 addition              |

| VPSUBQ zmm1 {k1}, zmm2, zmm3                       | INT64 subtraction           |

| <pre>VP{SRA,SRL,SLL}Q zmm1 {k1}, zmm2, imm8</pre>  | INT64 shift (imm8)          |

| <pre>VP{SRA,SRL,SLL}VQ zmm1 {k1}, zmm2, zmm3</pre> | INT64 shift (variable)      |

| <pre>VP{MAX,MIN}Q zmm1 {k1}, zmm2, zmm3</pre>      | INT64 max, min              |

| <pre>VP{MAX,MIN}UQ zmm1 {k1}, zmm2, zmm3</pre>     | UINT64 max, min             |

| VPABSQ zmm1 {k1}, zmm2, zmm3                       | INT64 absolute value        |

| <pre>VPMUL{DQ,UDQ} zmm1 {k1}, zmm2, zmm3</pre>     | 32x32 = 64 integer multiply |

### Math Support

Instruction

30

#### Package to aid with Math library writing

- Good value upside in financial applications

- Available in PS, PD, SS and SD data types

- Great in combination with embedded RC

#### VGETXEXP<sub>{PS,PD,SS,SD}</sub> Obtain exponent in FP format zmm1 {k1}, zmm2 VGETMANT {PS, PD, SS, SD} zmm1 {k1}, zmm2 Obtain normalized mantissa VRNDSCALE {PS.PD.SS.SD} zmm1 {k1}, zmm2, imm8 Round to scaled integral number VSCALEF {PS.PD.SS.SD} zmm1 {k1}, zmm2, zmm3 X\*2<sup>y</sup>, X <= getmant, Y <= getexp VFIXUPIMM<sub>{PS,PD,SS,SD}</sub> zmm1, zmm2, zmm3, imm8 Patch output numbers based on inputs Approx. reciprocal() with rel. error 2<sup>-14</sup> VRCP14{PS.PD.SS.SD} zmm1 {k1}, zmm2 VRSQRT14{PS,PD,SS,SD} zmm1 {k1}, zmm2 Approx. rsqrt() with rel. error 2<sup>-14</sup> VDIV<sub>{PS,PD,SS,SD}</sub> zmm1 {k1}, zmm2, zmm3 **IEEE division** VSQRT<sub>{PS.PD.SS.SD}</sub> zmm1 {k1}, zmm2 **IEEE** square root

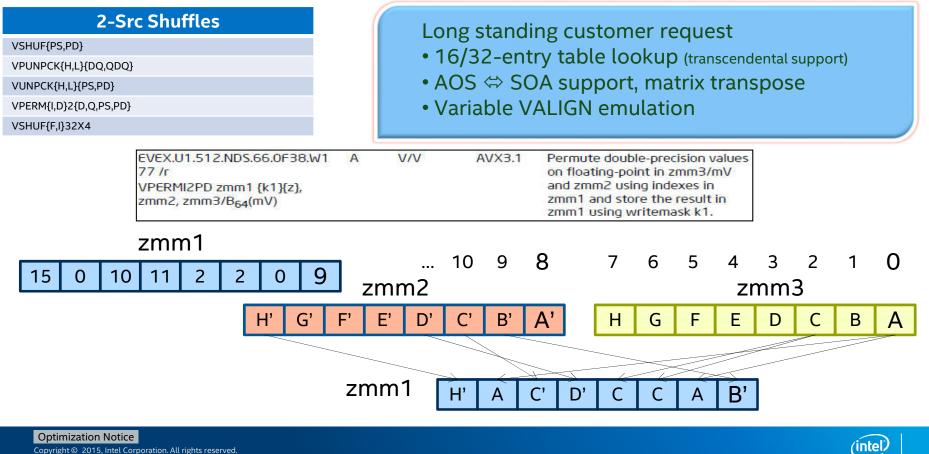

#### **New 2-Source Shuffles**

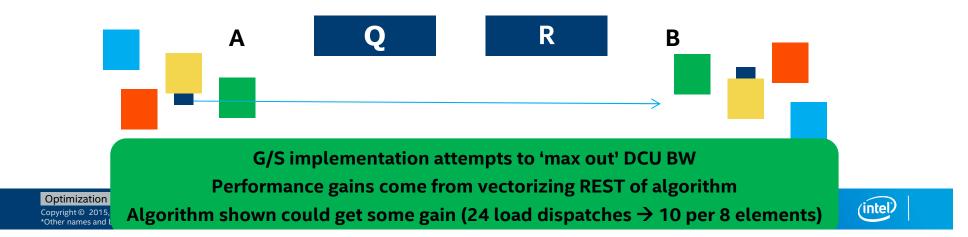

### **Gather & Scatter**

D/Q/SP/DP element types D/Q indices Instruction can partially execute k-reg Mask used as completion mask

VMOVDQU64 zmm1, Q[rsi]

VMOVDQU64 zmm2, R[rsi]

VGATHERQQ zmm0 {k2}, [rax+zmm1\*8]

VSCATTERQQ [rax+zmm2\*8] {k3}, zmm0

for(j=0, i=0; i<N; i++)

B[R[i]] = A[Q[i]];

### **Bit Manipulation**

Basic bit manipulation operations on mask and vector operands

- Useful to manipulate mask registers

- Have uses in cryptography algorithms

| Instruction                                      | Description                        |

|--------------------------------------------------|------------------------------------|

| KUNPCKBW k1, k2, k3                              | Interleave bytes in k2 and k3      |

| KSHIFT{L,R}W k1, k2, imm8                        | Shift bits left/right using imm8   |

| <pre>VPROR{D,Q} zmm1 {k1}, zmm2, imm8</pre>      | Rotate bits right using imm8       |

| <pre>VPROL{D,Q} zmm1 {k1}, zmm2, imm8</pre>      | Rotate bits left using imm8        |

| <pre>VPRORV{D,Q} zmm1 {k1}, zmm2, zmm3/mem</pre> | Rotate bits right w/ variable ctrl |

| <pre>VPROLV{D,Q} zmm1 {k1}, zmm2, zmm3/mem</pre> | Rotate bits left w/ variable ctrl  |

### **VPTERNLOG – Ternary Logic Instruction**

- Take every bit of three sources to obtain a 3-bit index N

- Obtain Nth bit from imm8

#### VPTERNLOGD zmm0 {k2}, zmm15, zmm3/[rax], imm8

Any arbitrary truth table of 3 values can be implemented *andor*, *andxor*, *vote*, *parity*, bitwise-*cmov*, etc each column in the right table corresponds to imm8

| <b>S1</b> | S2 | <b>S</b> 3 | ANDOR | VOTE | (S1)?S3:S2 |

|-----------|----|------------|-------|------|------------|

| 0         | 0  | 0          | 0     | 0    | 0          |

| 0         | 0  | 1          | 1     | 0    | 1          |

| 0         | 1  | 0          | 0     | 0    | 0          |

| 0         | 1  | 1          | 1     | 1    | 1          |

| 1         | 0  | 0          | 0     | 0    | 0          |

| 1         | 0  | 1          | 1     | 1    | 0          |

| 1         | 1  | 0          | 1     | 1    | 1          |

| 1         | 1  | 1          | 1     | 1    | 1          |

Imm8[7:0]

Src0[i]

Src1[i]

Src2[i]

Dest[i]

### AVX-512 ERI & AVX-512 PRI: Xeon Phi Only

### Xeon Phi Only Instructions

Set of segment-specific instruction extensions

- First appear on KNL

- Will be supported in all future Xeon Phi processors

- May or may not show up on a later Xeon processor

#### Address two HPC customer requests

- Ability to maximize memory bandwidth

- Hardware prefetching is too restrictive

- Conventional software prefetching results in instructions overhead

- Competitive support for transcendental sequences

- Mostly division and square root

- Differentiating factor in HPC/TPT

### KNL AVX512 additions

| CPUID     | Instructions           | Motivation                                                                                                    |  |

|-----------|------------------------|---------------------------------------------------------------------------------------------------------------|--|

| PRI       | PREFETCHWT1            | Reduce ring traffic in core-to-core data communication                                                        |  |

| AVX-512 F | VGATHERPF{D,Q}{0,1}PS  | Reduce overhead of software prefetching:<br>dedicate side engine to prefetch sparse structures while devoting |  |

| A         | VSCATTERPF{D,Q}{0,1}PS | ne main CPU to pure raw flops                                                                                 |  |

| ERI       | VEXP2{PS,PD}           | Speed-up key FSI workloads: Black-Scholes, Montecarlo                                                         |  |

| AVX-512 E | VRCP28{PS,PD}          | Key building block to speed up most transcendental sequences (in particular, division and square root):       |  |

| AV        | VRSQRT28{PS,PD}        | Increasing precision from 14=>28 allows to reduce one complete<br>Newton-Raphson iteration                    |  |

### Summary of AVX512 on KNL

#### AVX-512 F: new 512-bit vector ISA extension

Common between Xeon and Xeon Phi (KNL)

#### **AVX-512 CDI Conflict detection instructions**

- Improves autovectorization of Histogram data patterns

- On Xeon Phi first

#### AVX-512 ERI & PRI

- 28-bit transcendentals and new prefetch instructions

- On Xeon Phi only

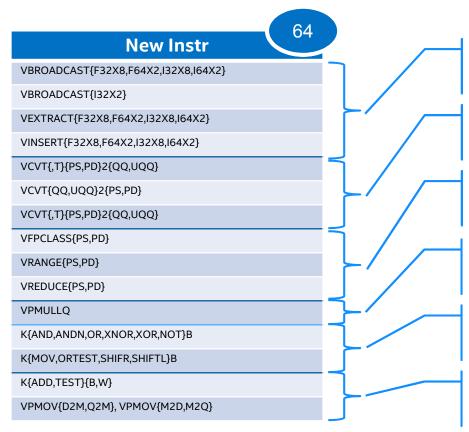

### Xeon additions to AVX512F

### AVX512DQ

Complete Qword support

- VPMULLQ packed 64x64 → 64

- Packed/Scalar converts of signed/unsigned to SP/DP

- Arithmatic shift right

- Etc

Extend mask architecture to word and byte

Byte masks are natural for packed Qword operands

Minor additions to transcendental support

Convert AVX512 mask  $\leftarrow \rightarrow$  'SSE/AVX' mask

- 'aggregate datatype' support

- Broadcast/insert/extract complex singles etc

### AVX512DQ : additional HPC focus

Tuple support: 32X8, 64X2, 32X2

Int64  $\Leftrightarrow$  FP conversions

Both unsigned and signed

Transcendental package v2

INT64 arithmetic support

Byte support for mask instructions

Expanded mask functionality

Optimization Notice

### AVX512BW

Full support for Byte/Word operations

MMX/SSE2/AVX2 re-promoted to AVX512 semantics

Mask operations extended to 32/64 bits

- 32-bit mask refers to AVX512 'short' operands

- 64-bit mask refers to AVX512 byte operands

Loads/Stores/Broadcastsfor AVX512 semantics

Permute architecture extended to words

Vpermw, vpermi2w, vpermt2w

New PSAD instruction, etc

### AVX512BW : Byte and Word Support

| AV512BW               | AV512BW                  | AV512BW                |

|-----------------------|--------------------------|------------------------|

| VPBROADCAST{B,W}      | KTEST{D,Q}               | VPSHUFB, VPSHUF{H,L}W  |

| VPSRLDQ, VPSLLDQ      | KSHIFT{L,R}{D,Q}         | VP{SRA,SRL,SLL}{,V}{W} |

| VP{SRL,SRA,SLL}{V}W   | KUNPACK{WD,DQ}           | VPUNPCK{H,L}{BW,WD}    |

| VPMOV{WB,SWB, USWB}   | KADD{D,Q}                |                        |

| VPTESTM{B,W}          | VPMOV{B2M,W2M,M2B,M2W}   |                        |

| VPMADW                | VPCMP{,EQ,GT}{B,W,UB,UW} |                        |

| VPTESTNM{B,W}         | VP{ABS,AVG}{B,W}         |                        |

| VDBPSADBW             | VP{ADD,SUB}{,S,US}{B,W}  |                        |

| VPERMW, VPERM{I,T}2W  | VPALIGNR                 |                        |

| VMOVDQU{8,16}         | VP{EXTR,INSR}{B,W}       |                        |

| VPBLENDM{B,W}         | VPMADD{UBSW,WD}          |                        |

| {KAND,KANDN}{D,Q}     | VP{MAX,MIN}{S,U}{B,W}    |                        |

| {KOR,KXNOR,KXOR}{D,Q} | VPMOV{SX,ZX}BW           |                        |

| KNOT{D,Q}             | VPMUL{HRS,H,L}W          |                        |

| KORTEST{D,Q}          | VPSADBW                  |                        |

### AVX512VL : Vector Length Orthogonality

Allow AVX512 instructions to operate on sub-vectors (lower 256/128 bits)

- Eases code generation for mixed data types

- Partial masks are functionally correct, why not use them?

- VL is in static in opcode, provides information EARLY in pipeline

- Clock gating of unneeded execution elements / buses

- Disabling RF read ports

- Preventing 'false overlap/forwarding' from being detected in memory

- Creating partial masks wastes instruction BW

#### AVX512VL is NOT a "list of instructions"

- "orthogonal feature' applying to "all" AVX512 instructions

- obvious caveats when instruction has implicit 256/512 width

### AVX512VL : Down-promotions

| 318 Out of 450 AVX512 Instructions |                               |                                |  |  |  |  |

|------------------------------------|-------------------------------|--------------------------------|--|--|--|--|

| VL orthogonality                   |                               |                                |  |  |  |  |

| V{ADD,MUL,SUB}{PS,PD}              | VF{N}MADD{132,213,231}{PS,PD} | VPERMIL{PS,PD}, VSHUF{PS,PD}   |  |  |  |  |

| VALIGN{D,Q}                        | VF{N}MSUB{132,213,231}{PS,PD  | VP{MAX,MIN}{D,Q,UD,UQ}         |  |  |  |  |

| VBLENDM{PS,PD}, VPBLENDM{D,Q}      | VFMADDSUB{132,213,231}{PS,PD} | VPMOX{SX,ZX}{B,W}{D,Q}         |  |  |  |  |

| VBROADCAST{SS,SD,F32X4,I32X4}      | VFMSUBADD{132,213,231}{PS,PD} | VPMOX{SX,ZX}DQ                 |  |  |  |  |

| VCMP{SS,SD}                        | VGATHER{D,Q}{PS,PD}           | VPMUL{DQ,UDQ,LD}               |  |  |  |  |

| VCOMPRESS{PS,PD}, VPCOMPRESS{D,Q}  | VPGATHER{D,Q}{D,Q}            | VP{SLL,SRL,SRA}{,V}{D,Q}       |  |  |  |  |

| VCVT{DQ,UDQ}2{PS,PD}               | V{MAX,MIN}{PS,PD}             | VPTESTM{D,Q}                   |  |  |  |  |

| VCVT{,T}{PS,PD}2{DQ,UDQ}           | VMOV{APS,UPS,DQA32,DQA64}     | VPUNPCK{H,L}{DQ,QDQ}           |  |  |  |  |

| VCVT{PS2PD,PD2PS}                  |                               |                                |  |  |  |  |

| VCVT{PS2PH, Etc pro                | bably more than are s         | shown                          |  |  |  |  |

| VDIV{PS,PD}                        | VP{AB5,ADD,50B}{D,Q}          | VPTERNLOG{D,Q}                 |  |  |  |  |

| VEXPAND{PS,PD}, VPEXPAND{D,Q}      | VP{AND,ANDN,OR,XOR}{D,Q}      | VPMOVQ{,S,US}Q{QB,QW,QD,DB,DW} |  |  |  |  |

| VEXTRACT{F32X4,I32X4}              | VPCMP{,EG,GR}{D,Q,UD,UQ}      | VSHUF{F32X4,F64X2,I32X4,I64X2} |  |  |  |  |

| V{MAX,MIN}{PS,PD}                  | VPERM{D,Q,PS,PD}              | VPERM{T,I}2{D,Q,PS,PD}         |  |  |  |  |

# Summary of Xeon AVX512 Additions

### More Qword support

Packed converts, VPMULLQ etc

Support for mixing AVX and AVX512 style masks

- VPMOVM2\*, VPMOV\*2M

- All HLL datatypes at maximum SIMD width

- # elements = VL / element\_size

- VL aids mixing datatypes

- VL = # elements \* element\_size

- VL specifies memory access sizes exactly

- Masks provide architectural support, but HW prefers a 'static' knowledge

### Summary

AVX512 is a comprehensive addition to intels SIMD Instruction set ~2x performance on BLAS routines new features to increase the vectorization coverage (masks, VPCOMRESS) embedded rounding and new instructions accelerate math libraries Knights Landing emphasis on HPC support for D/Q/SP/DP and additional specialized instructions Xeon adds support for all HLL datatypes

AVX512 is designed for compilers as well as programmers

# PUTTING EXPLICIT VECTOR PROGRAMMING TO WORK FOR INTEL XEON AND XEON PHI ARCHITECTURES

Xinmin Tian – Senior Principal Engineer Intel Compiler and Languages, SSG, Intel Corporation September 11, 2016

PACT 2016 Tutorial, Haifa, Israel

# Section II: Agenda

Seamless Vectorization and Parallelization Integration Showcase

Learnings: Cray\*, Intel<sup>®</sup> Pentium<sup>®</sup> 4 (90nm) SSE3 and SIMD Vectorization Hurdles

Successes: Putting SIMD Vectorization to Work

- Mixed data type Vectorization

- ✓ Function vectorization

- Outer loop vectorization

- ✓ SIMD Loop Vectorization with Cross-iteration Dependency

- ✓ Less-than-full-vector Vectorization

- Predication and Masking

- ✓ Gather/Scatter Optimization

Advances: Tackle C++ Challenges and Beyond C/C++/Fortran

Summary: Close to Metal Performance

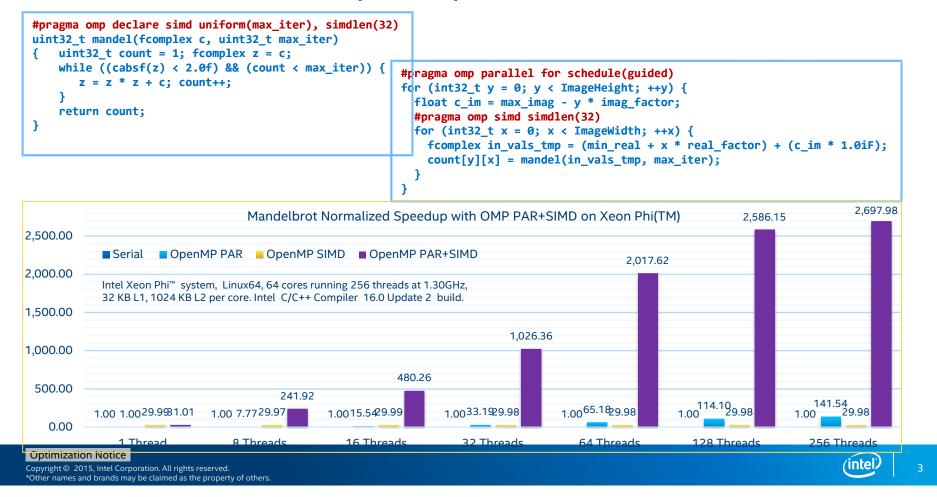

### Mandelbrot: ~2698x Speedup on Xeon Phi<sup>™</sup>--Isn't it Cool?

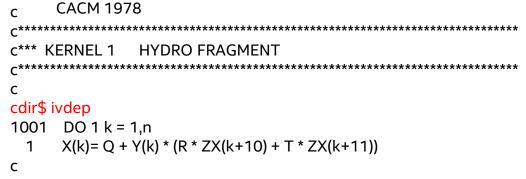

### Learnings: Compiler Vectorization in 1978

The CRAY-1's Fortran compiler (CFT) is designed to give the scientific user immediate access to the benefits of the CRAY-1's vector processing architecture. An optimizing compiler, CFT, "vectorizes" innermost DO loops. Compatible with the ANSI 1966 Fortran Standard and with many commonly supported Fortran extensions, CFT does not require any source program modifications or the use of additional nonstandard Fortran statements to achieve vectorization. Thus the user's investment of hundreds of man months of effort to develop Fortran programs for other contemporary computers is protected.

Livermore loop #1 Small loop, simple data and control flow

Compiler auto-vectorization becomes reality through dependency analysis

Compiler vectorization "solved" in 1978

Optimization Notice

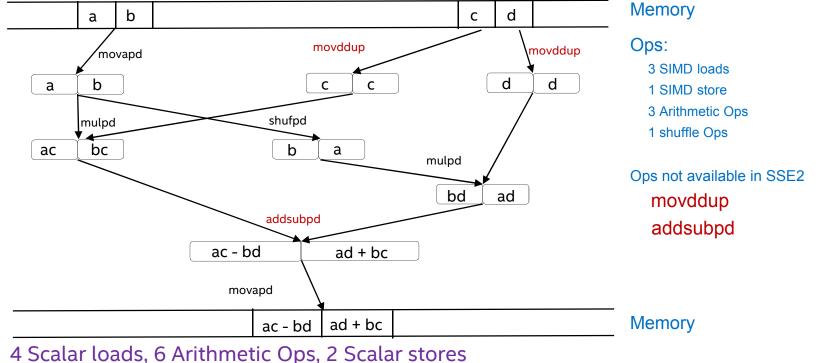

### Learnings: 2004 Intel® Pentium® 4 SSE3 on 90nm

Complex Multiplication with SSE3: (a + ib)(c + id) = (ac - bd) + i(ad + bc)

Performance can be improved up to ~75%, SPEC2000FP/168.wupwise 10-15%

### Learnings: Program Factors Impact on Vectorization

Loop-carried dependencies

DO I = 2, N A(I) = A(I-1) + B(I) ENDDO

Function calls

for (i = 1; i < nx; i++) {

x = x0 + i \* h;

sumx = sumx + func(x, y, xp);

}</pre>

Pointer aliasing

```

void scale(int *a, int *b)

{

for (int i = 0; i < 1000; i++)

b[i] = z * a[i];

}</pre>

```

<u>many .....</u>

Optimization Notice Copyright © 2015, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others. Unknown loop iteration count

```

struct _x { int d; int bound; };

void doit(int *a, struct _x *x)

{

for(int i = 0; i < x->bound; i++)

a[i] = 0;

}

```

Indirect memory access

for (i=0; i<N; i++)

A[B[i]] += C[i]\*D[i]</pre>

### Outer loops

```

for(j = 0; j <= MAX; j++) {

for(i = 0; i <= MAX; i++) {

D[i][j] += 1;

}

}</pre>

```

### Learnings: SIMD Vectorization Hurdles

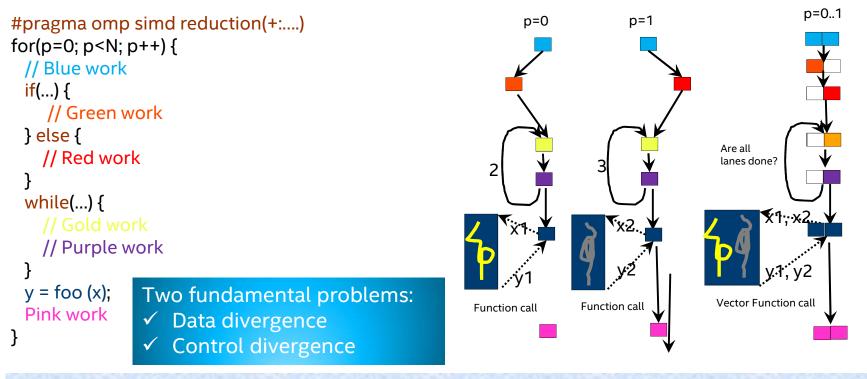

Vector code generation has become a more difficult problem increasing need for user guided explicit vectorization that maps concurrent execution to simd hardware

# Successes: Putting SIMD Vectorization to Work

Intel brings ICC Vectorization Technology to LLVM Vectorizer

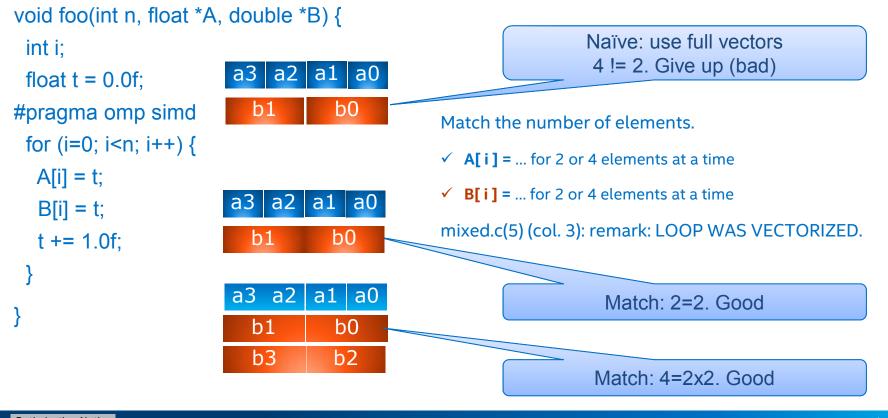

# Mixed Data Type Vectorization

Optimization Notice Copyright © 2015, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

(intel)

47

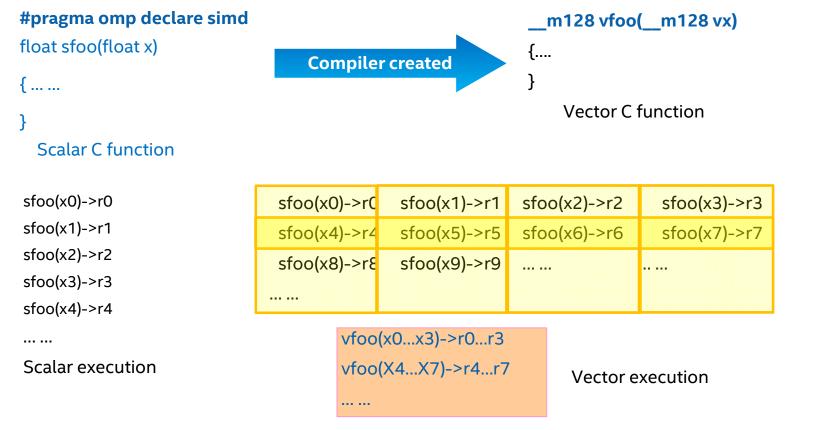

# **Function Vectorization**

### **Recursive Function Vectorization**

```

#pragma omp declare simd [processor(cpu-id)]

int binsearch(int key, int lo, int hi) {

int ans;

if (lo > hi) \{

ans = -1;

}

else {

int mid = lo + ((hi - lo) >> 1);

int t = sortedarr[mid];

if (key == t) {

ans = mid;

}

else if ( key > t) {

ans = binsearch(key, mid + 1, hi);

}

else {

ans = binsearch(key, lo, mid - 1);

}

}

return ans;

}

#pragma omp simd

for (int i=0; i<M; i++) {</pre>

ans[i] = binsearch(keys[i], 0, N-1);

}

```

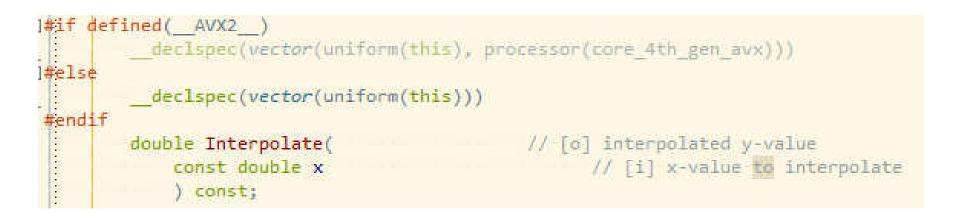

# **OpenMP\* SIMD PROCESSOR Clause**

New **PROCESSOR** clause extension to **#pragma omp declare simd** (to define a SIMD routine) to target a specific processor

- Similar to Intel<sup>®</sup> Cilk<sup>™</sup> Plus extensions for declaring SIMD functions

- Available for C/C++ and Fortran

- Intel extension NOT part of official OpenMP specification

- Helpful to allow programmers to leverage e.g. Intel<sup>®</sup> AVX-2 and Intel<sup>®</sup> AVX-512 beyond default Intel<sup>®</sup> SSE2 support (YMM+ZMM registers/operands additionally to XMM )

# **Processor Name Identifiers**

✓ pentium\_4

✓ pentium\_m

✓ pentium\_4\_sse3

✓ core\_2\_duo\_ssse3

✓ core\_2\_duo\_sse4\_1

✓ atom

✓ core\_i7\_sse4\_2

✓ core\_aes\_pclmulqdq

✓ core\_2nd\_gen\_avx

✓ core\_3rd\_gen\_avx

| <ul> <li>✓ future_cpu_18</li> <li>✓ mic</li> </ul> | // KNF          |

|----------------------------------------------------|-----------------|

| ✓ future cpu 19                                    | // KNC          |

| <pre>✓ future_cpu_20</pre>                         | // HSW - no TSX |

| ✓ core_4th_gen_avx                                 | // HSW – no TSX |

| ✓ core_4th_gen_avx_tsx                             | // HSW - TSX    |

| ✓ future_cpu_21                                    | // BDW - NO TSX |

| ✓ future_cpu_21_tsx                                | // BDW - TSX    |

| ✓ future_cpu_22                                    | // KNL          |

| ✓ future_cpu_23                                    | // SKL          |

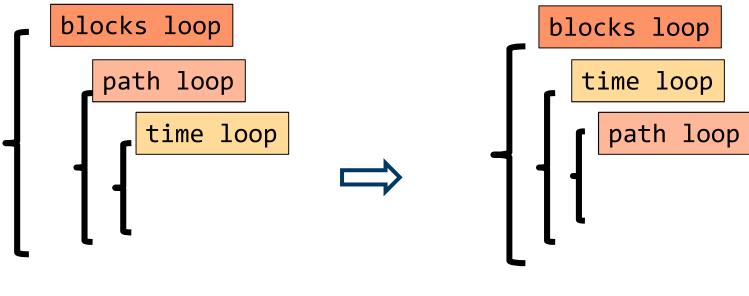

# Vortex Code: Outer Loop Vectorization

```

#pragma omp simd // simd pragma for outer-loop at call-site of SIMD-function

for (int i = beg*16; i < end*16; ++i) {

particleVelocity block(px[i], py[i], pz[i], destvx + i, destvy + i, destvz + i, vel block start, vel block end);

}

```

#pragama omp declare simd linear(velx,vely,velz) uniform(start,end) aligned(velx:64, vely:64, velz:64) static void particleVelocity block(const float posx, const float posy, const float posz,

float \*velx, float \*vely, float \*velz, int start, int end) {

```

for (int j = start; j < end; ++j) {

const float del p x = posx - px[i];

const float del p y = posy - py[i];

const float del p z = posz - pz[j];

const float dxn= del p x * del p x + del p y * del p y + del p z * del p z + pa[i]* pa[i];

const float dxctaui = del p y * tz[i] - ty[i] * del p z;

const float dyctaui = del p z * tx[i] - tz[i] * del p x;

const float dzctaui = del p x * ty[i] - tx[i] * del p y;

const float dst = 1.0f/std::sqrt(dxn);

KNC performance improvement

const float dst3 = dst*dst*dst:

over 2X going

*velx

-= dxctaui * dst3:

from inner to outer-loop vectorization

-= dyctaui * dst3;

*velv

-= dzctaui * dst3;

*velz

```

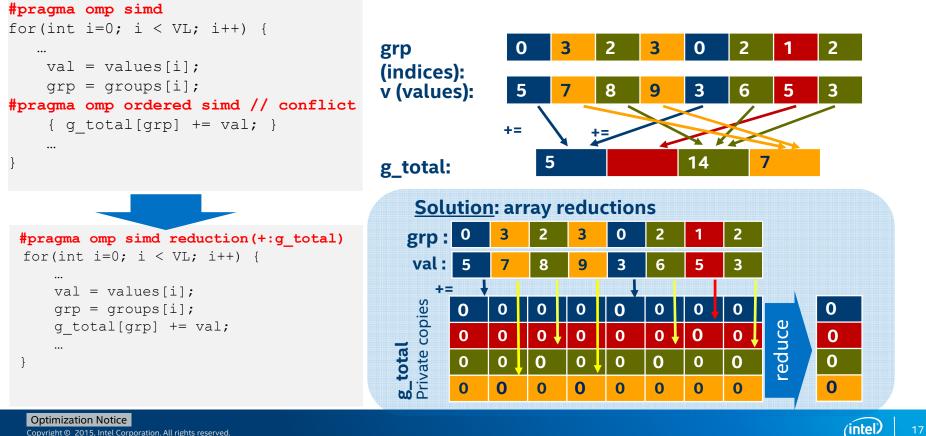

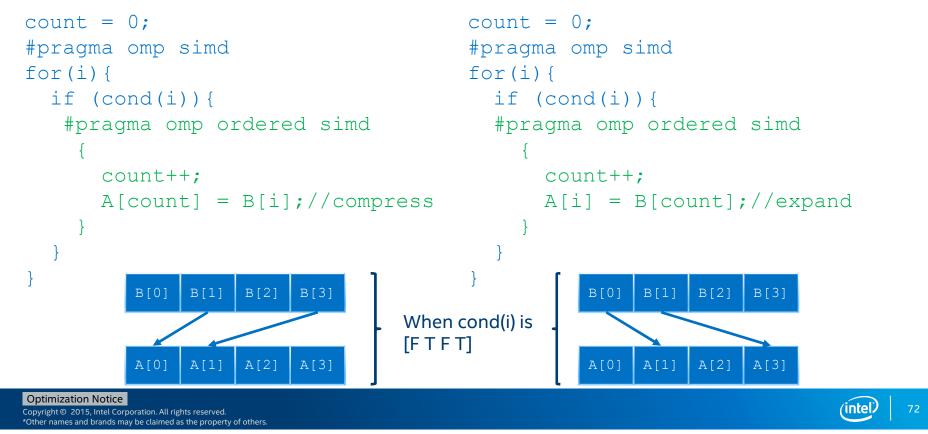

# SIMD Loops with Cross-Iteration Dependencies

OpenMP\* 4.5: Extend ordered Blocks in SIMD Contexts

### C and C++:

#pragma omp ordered [simd]

structured code block

### Fortran:

!\$omp ordered [simd]

structured code block

!\$omp end ordered

### Semantics:

• The ordered with simd clause construct specifies a structured block in the simd loop or SIMD function that will be executed in the order of the loop iterations w.r.t to dependency constraints or sequence of call to SIMD functions.

### Rules:

- #pragma omp ordered simd is only allowed inside a SIMD loop or SIMD-enabled function.

- #pragma omp ordered simd region must be a single-entry and single-exit code block

- The strict ordered execution is only guaranteed for the block itself

- ✓ Execution remains weakly ordered w.r.t. to outside of the block or other ordered blocks

- $\checkmark$  Data dependencies between statements of the same block will be correctly resolved

- $\checkmark$  Other non-vector dependencies originating in ordered block still lead to undefined behavior

# **Ordered SIMD Examples**

### OK:

```

#pragma omp simd

for (i = 0; i < N; i++)

{

. . .

#pragma omp ordered simd

a[indices[i]] += b[i]; // index conflict

}

#pragma omp ordered simd

{

if (c[i] > 0)

q[j++] = b[i]; // compress pattern

}

. . .

#pragma omp ordered simd

{

lock(L)

// atomic update

if (x > 10) x = 0;

unlock(L)

}

. . .

```

### Not OK w.r.t serial:

| <pre>#pragma omp simd for (i = 0; i &lt; N; i++) { #pragma omp ordered simd {</pre>                  | Compiler<br>won't<br>complain! |

|------------------------------------------------------------------------------------------------------|--------------------------------|

| <pre>if (c[i] &gt; 0)         q[j++] = b[i]; // 1<sup>st</sup> comp } #pragma omp ordered simd</pre> | press                          |

| <pre>{      // 2<sup>nd</sup> comp<br/>if (c[i] &gt; 0)</pre>                                        | of stores will                 |

### **ORDERED SIMD not always best Approach**

### Less-Than-Full-Vector Vectorization

```

float foo(float *y, int n)

{ int k; float x = 10.0f;

#pragma omp simd

for (k = 0; k < n; k++) {

x = x + fsqrt(y[k])

}

return x

}</pre>

```

```

misalign = &y[0] & 63

peeledTripCount = (63 - misalign)/sizeof(float)

x = 10.0f:

do k0 = 0, peeledTripCount-1 // peeling loop

x = x + fsqrt(y[k0])

enddo

x1 v512 = (m512)0

x2 v512 = (m512)0

mainTripCount = n - ((n - peeledTripCount) \& 31)

do k1 = peeledTripCount, mainTripCount-1, 32

x1_v512 = _mm512_add_ps(_mm512_fsqrt(y[k1:16]),x1_v512)

x_2 v_{512} = mm_{512} add ps(mm_{512} fsqrt(y[k_{1+16:16}]), x_2 v_{512})

enddo

// perform vector add on two vector x1_v512 and x2_v512

x1 v512 = mm512 add ps(x1 v512, x2 512);

// perform horizontal add on all elements of x1_v512, and

// the add x for using its value in the remainder loop

x = x + mm512 hadd ps(x1 512)

do k2 = mainTripCount, n // Remainder loop

x = x + fsqrt(y[k2])

```

enddo

### Less-Than-Full-Vector Vectorization

misalign = &y[0] & 63

peeledTripCount = (63 - misalign) / sizeof(float)

x = 10.0f;

// create a vector: <0,1,2,...15>

k0\_v512 = \_mm512\_series\_pi(0, 1, 16)

#### // create vector: all 16 elements are peeledTripCount

```

mainTripcount = n - ((n - peeledTripCount) & 31)

do k1 = peeledTripCount, mainTripCount-1, 32

x1_v512 = _mm512_add_ps( _mm512_fsqrt(y[k1:16]), x1_v512)

x2_v512 = _mm512_add_ps( _mm512_fsqrt(y[k1+16:16]), x2_v512)

enddo

```

// create a vector: <mainTripCount, mainTripCount+1 ... mainTripCount+15>

k2\_v512 = \_mm512\_series\_pi(mainTripCount, 1, 16)

```

// create a vector: all 16 elements has the same value n

n_v512 = _mm512_broadcast_pi32(n)

step_v512 = _mm512_broadcast_pi32(16)

```

```

x1_v512 = _mm512_add_ps(x1_v512, x2_512);

```

// perform horizontal add on 8 elements and final reduction sum to write

// the result back to x.

Optimization Notice Copyright © 2015, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

= x + \_mm512\_hadd\_ps(x1\_512

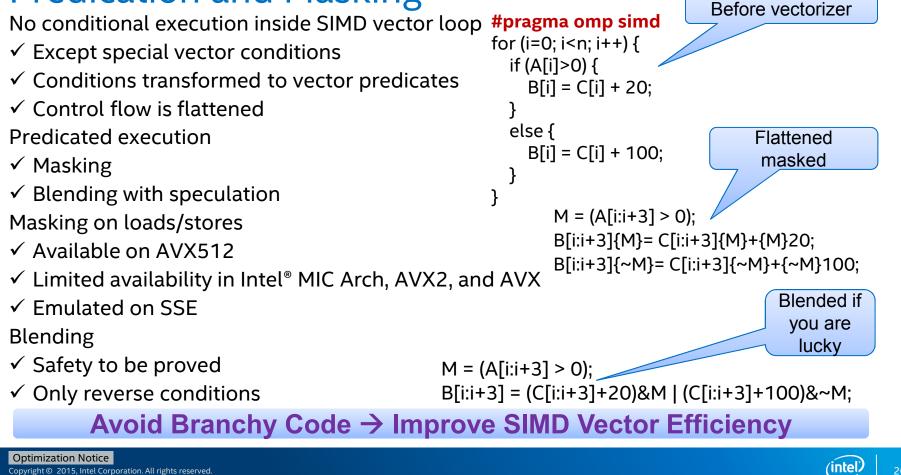

# **Predication and Masking**

Other names and brands may be claimed as the property of others

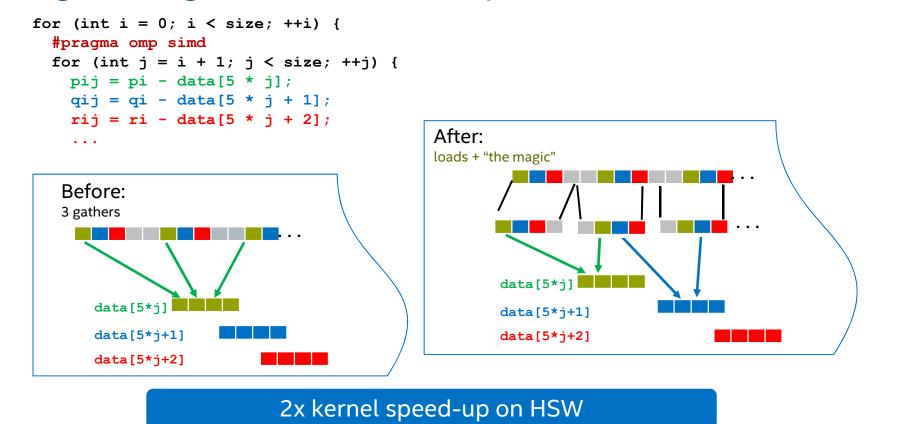

### **Neighboring Gather/Scatter Optimization**

Optimization Notice

Copyright © 2015, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others. 21

(intel)

### **Optimization of neighboring Gathers**

- Complete support for unmasked strided (d[i]) and indexed (d[ind[i]]) loads of 1, 2, 4, 8 and 16-byte elements for SSE2-AVX512

- Provides more effective CPU resources usage for cases with data locality

- May require additional source changes to enable the pattern recognition (e.g. restrict, base/index hoisting, loads grouping)

- Also reflected in optimization report:

```

remark #34030: adjacent sparse (strided) loads

optimized for speed.

Details: stride { 12 }, types { F32-V512, F32-

V512, F32-V512 }, number of elements { 16 },

select mask { 0x00000007 }.

```

Optimization Notice Copyright © 2015, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others

```

struct {

TYPE f0;

...

TYPE fN;

} d[];

for (int i = 0; i < size; ++i)</pre>

```

tmp += d[i].f0 + ... + d[i].fN;

#### Before (TYPE=FLOAT, N=2)

| vgatherdps | 0(%rcx,%zmm0,4), | %zmm6{%k1} |

|------------|------------------|------------|

| vgatherdps | 4(%rcx,%zmm0,4), | %zmm7{%k2} |

| vgatherdps | 8(%rcx,%zmm0,4), | %zmm9{%k3} |

#### Now (TYPE=FLOAT, N=2)

| vmovups   | (%rcx), %zmm10                   |

|-----------|----------------------------------|

| vmovups   | 64(%rcx), %zmm9                  |

| vmovups   | 128(%rcx), %zmm14                |

| vpermi2ps | %zmm9, %zmm10, %zmm7             |

| vpermi2ps | %zmm9, %zmm10, %zmm8             |

| vpermt2ps | %zmm9, %zmm1, %zmm10             |

| vpermi2ps | %zmm7, %zmm14, %zmm11            |

| vpermi2ps | <pre>%zmm8, %zmm14, %zmm12</pre> |

| vpermt2ps | <pre>%zmm10, %zmm0, %zmm14</pre> |

|           |                                  |

60

# OpenMP SIMD Linear(ref/val/uval)

Rationale:

• For implicitly reference linear parameters it is nice to have reference as linear

OpenMP 4.5 syntax:

- Linearity specification for references vs. values

- linear(val(var):[step]) the value is linear even if passed by reference

- If passed by reference the vector of references is passed

- linear(uval(var):[step]) value passed by reference is linear

- The reference to the first lane is passed, other values constructed using step

- linear(ref(var):step) for parameters passed by reference the underlying reference is linear

- Access will be sequential or strided depending on step

- Original linear(var:[step]) the same as linear(val(var):[step])

```

!$omp declare simd

REAL FUNCTION FOO(X, Y)

REAL, VALUE :: Y << by reference

REAL, VALUE :: X << by reference

FOO = X + Y << gathers!!!!

END FUNCTION FOO

...

!omp$ simd private(X,Y)

DO I= 0, N

Y = B(I)

X = A(I)

C(I) += FOO(X, Y)

ENDDO

```

```

!$omp declare simd linear(ref(x),ref(y))

REAL FUNCTION FOO(X, Y)

REAL, VALUE :: Y << by reference

REAL, VALUE :: X << by reference

FOO = X + Y << sequential reads

END FUNCTION FOO

...

!omp$ simd private(X,Y)

DO I= 0, N

Y = B(I)

X = A(I)

C(I) += FOO(X, Y)

ENDDO</pre>

```

# Linear(ref/val/uval) Examples

### Things to remember:

- linear(ref(x:[step])) matches to unit/non-unit stride arguments if step match

- linear(ref(x)) matches to private arguments: these are allocated sequentially

- linear(uval(x)) is preferred to linear(val(x)) for by-reference passed read-only linears: uval facilitates more efficient parameter passing. If both specified uval is matched

#### linear(ref):

```

#pragma omp declare simd linear(ref(p))

void add_one(int& p) { p += 1; }

int a[NN];

#prgma omp simd linear(p)

for (i = 0; i < NN; i++) {

add_one(*p); <<< unit-stride load</pre>

p++;

}

#prgma omp simd private(p)

for (i = 0; i < NN; i++) {

p = a[i];

add_one(p); <<< private

b[i] = p;

}

#prgma omp simd

for (i = 0; i < NN; i++) {</pre>

add_one(i); <<< match, incorrect</pre>

}

```

Optimization Notice Copyright © 2015, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

#### Linear(val)/linear(uval):

```

interface

real function func1(x, i)

!$omp declare simd(func1) uniform(x) linear(val(i):1)

real(8), intent(inout) :: x(*)

integer, intent(in), value :: i

end function func1

real function func2(x, i)

!$omp declare simd(func2) uniform(x) linear(uval(i):1)

real(8), intent(inout) :: x(*)

integer, intent(in), value :: i

end function func2

end interface

!$omp simd linear(k:1)

do i=1, n

x(i) = func1(x, k) \ll k passed as vector of refs

x(i) = func2(x, k) \ll k passed as single ref

k = k + 1

enddo

```

intel

# SIMD Data Layout Template (SDLT) Library

```

#include <stdio.h>

#include <stdio.h>

#include <sdlt/primitive.h>

#include <iostream>

#include <sdlt/soa1d_container.h>

#define N 1024

#define N 1024

typedef struct RGBs {

typedef struct RGBs {

float r; float g; float b;

float r; float g; float b;

} RGBTy;

} RGBTv;

rgbrgbrgbm

SDLT_PRIMITIVE(RGBTy, r, g, b)

void main()

void main()

{

RGBTy a[N];

auto a = aContainer.access();

#pragma omp simd

#pragma omp simd

for(int k=0; k<N; k++) {

for(int k=0; k<N; k++) {

a[k].r = k*1.5; a[k].g = k*2.5; a[k].b = k*3.5;

}

std::cout << "k =" << 10 <<

", a[k].r =" << a[10].r <<

std::cout << "k =" << 10 <<

", a[k].g =" << a[10].g <<

", a[k].r =" << a[10].r() <<

", a[k].b =" << a[10].b << std::endl;

", a[k].g =" << a[10].g() <<

}

```

**Optimization Notice** Copyright © 2015, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others

g g g g b b b b ... sdlt::soa1d container<RGBTy>aContainer(N); a[k].r() = k\*1.5; a[k].g() = k\*2.5; a[k].b() = k\*3.5;", a[k].b =" << a[10].b() << std::endl;

### SDLT: AOS vs. SOA

#### AOS AVX512 ASM Code

| B1.3:     | # PredsB1.3B1.2                   |       |

|-----------|-----------------------------------|-------|

| vcvtdq2ps | %zmm5, %zmm11 #18.15              |       |

| lea       | (%rsp,%rax), %rcx #18.6           |       |

| vcvtdq2ps | %zmm4, %zmm12 #18.15              |       |

| vpaddd    | %zmm6, %zmm5, %zmm5 #16.3         |       |

| vpaddd    | %zmm6, %zmm4, %zmm4 #16.3         |       |

| vmulps    | %zmm11, %zmm3, %zmm7 #18.17       |       |

| vmulps    | %zmm12, %zmm3, %zmm8 #18.17       |       |

| vmulps    | %zmm11, %zmm2, %zmm9 #19.17       |       |

|           | %zmm12, %zmm2, %zmm10 #19.17      |       |

| vmulps    | %zmm11, %zmm1, %z #20.17          |       |

| vmulps    | %zmm12, %zmm1, %zmm1 #20.17       |       |

| kxnorw    | %k0, %k0, %k1 #18.6               |       |

| kxnorw    | %k0, %k0, %k2 #18.6               |       |

| kxnorw    | %k0, %k0, %k3 #19.6               |       |

| kxnorw    | %k0, %k0, %k4 #19.6               |       |

| kxnorw    | %k0, %k0, %k5 #20.6               |       |

| kxnorw    | %k0, %k0, %k6 #20.6               |       |

| vscatterd | ps %zmm7, (%rcx,%zmm0,4){%k1}     | #18.6 |

| vscatterd | ps %zmm8, 192(%rcx,%zmm0,4){%k2}  | #18.6 |

| addl      | \$32, %edx #17.12                 |       |

| lea       | 4(%rsp,%rax), %rsi                | #18.6 |

| vscatterd | ps %zmm9, (%rsi,%zmm0,4){%k3}     | #19.6 |

| lea       | 8(%rsp,%rax), %rdi                | #18.6 |

| vscatterd | ps %zmm10, 192(%rsi,%zmm0,4){%k4} | #19.6 |

| vscatterd | ps %zmm13, (%rdi,%zmm0,4){%k5}    | #20.6 |

| vscatterd | ps %zmm14, 192(%rdi,%zmm0,4){%k6} | #20.6 |

| addq      | \$384, %rax #17.12                |       |

| cmpl      | \$1024, %edx #17.12               |       |

| jb        | B1.3 # Prob 82% #17.12            |       |

#### Optimization Notice Copyright © 2015, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

#### SOA / SDLT AVX512 ASM Code: scatter instructions are all gone

| B1.5:     | # PredsB1.5                        | B1.4   |

|-----------|------------------------------------|--------|

| vpaddd    | %zmm4, %zmm3, %zmm12               | #19.3  |

| vcvtdq2ps | %zmm3, %zmm7                       | #21.17 |

| vcvtdq2ps | %zmm12, %zmm10                     | #21.17 |

| vmulps    | %zmm7, %zmm2, %zmm5                | #21.19 |

| vmulps    | %zmm7, %zmm1, %zmm6                | #22.19 |

| vmulps    | %zmm7, %zmm0, %zmm8                | #23.19 |

| vmulps    | %zmm10, %zmm2, %zmm3               | #21.19 |

| vmulps    | %zmm10, %zmm1, %zmm9               | #22.19 |

| vmulps    | %zmm10, %zmm0, %zmm11              | #23.19 |

| vmovups   | <pre>%zmm5, (%rsi,%rcx,4)</pre>    | #21.15 |

| vmovups   | <pre>%zmm6, (%rdx,%rcx,4)</pre>    | #22.15 |

| vmovups   | <pre>%zmm8, (%rax,%rcx,4)</pre>    | #23.15 |

| vmovups   | <pre>%zmm3, 64(%rsi,%rcx,4)</pre>  | #21.15 |

| vmovups   | <pre>%zmm9, 64(%rdx,%rcx,4)</pre>  | #22.15 |

| vmovups   | <pre>%zmm11, 64(%rax,%rcx,4)</pre> | #23.15 |

| vpaddd    | %zmm4, %zmm12, %zmm3               | #19.3  |

| addq      | \$32, %rcx                         | #21.6  |

| cmpq      | \$1024, %rcx                       | #21.6  |

| jb        | B1.5 # Prob 82%                    | #21.6  |

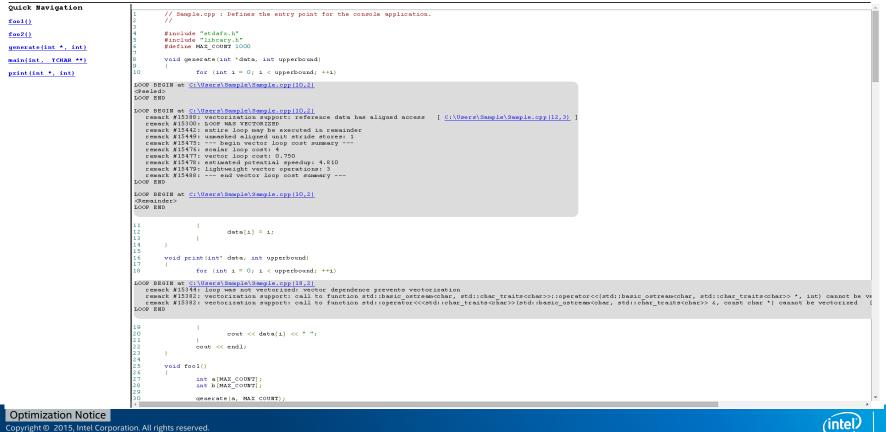

### **Programmer Friendly Optimization Report**

Annotated source listing with compiler optimization reports File: C:\Users\Sample\Sample.cpp

\*Other names and brands may be claimed as the property of others.

30

# **Optimization Report Improvements**

### ✓ Significant improvement in variable names and memory references reporting

- **16.0:** remark #15346: vector dependence: assumed ANTI dependence between line 108 and line 116

- 17.0: remark #15346: vector dependence: assumed ANTI dependence between \*(s1) (108:2) and \*(r+4) (116:2)

### More precise non-vectorization reasons

E.g.: "exception handling for function call prevents vectorization"

### ✓ Gather and partial scalarization reasons reporting (-qopt-report:5)

**16.0:** remark #15328: vectorization support: gather was emulated for the variable xyBase: indirect access [scalar\_dslash\_fused.cpp(334,27)]

17.0: remark #15328: vectorization support: gather was emulated for the variable

<xyBase[xbOffset][c][s][1]>, indirect access, part of index is conditional

[scalar\_dslash\_fused.cpp(334,27)]

### Other reasons are:

- read from memory

- nonlinearly computed

- o is result of a call to function

- is linear but may overflow ← either in unsigned indexing or in address computation

- **IS private** ← memory privatization in explicit vectorization or serialized computation

Optimization Notice

# **Vectorization Advisor**

### Assist code vectorization for Intel<sup>®</sup> SIMD (Zakhar A. Matveev)

- ✓ All the data you need in one place

- ✓ Combines Intel Compiler opt-report with dynamic profile.

- ✓ Detects "hot" unvectorized or "under vectorized" loops.

- ✓ Identify performance penalties and recommend fixes

- ✓ Explicit advices with "true intelligence" including **OpenMP4.x**

- ✓ Memory layout (stride) analysis

- ✓ Increase the confidence that vectorization is safe

| <b>Optimization Notice</b>   |                                         |

|------------------------------|-----------------------------------------|

| Copyright © 2015, Intel Corp | oration. All rights reserved.           |

| *Other names and brands ma   | y be claimed as the property of others. |

| Function Call Sites and Loops           | Self Time T                                        | ne 🔻 Total Time     |                  | ø      | Compiler Vectoriza                                                                                                                                                                                       | ization 📧 Vectorized Loops                                                                                                                                 |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |                          |              |

|-----------------------------------------|----------------------------------------------------|---------------------|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|--------------|

| ranction can sites and coops            |                                                    | . star rime         | Analysis         |        | Loop Type                                                                                                                                                                                                | Why No Ve                                                                                                                                                  | Gain Estimate                                                                                                        | Vecto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Vectorization             | n Traits                 |              |

| 🛛 🚺 [loop at nbody.cc:57 in main]       | 1,820s 🚍                                           | 1,820s 📼            |                  |        | <expand see<="" th="" to=""><th><expand t<="" th=""><th><expand s<="" th="" to=""><th>AVX</th><th>Square Roo</th><th>ts; Inserts; Extracts;</th><th>Masked Sto</th></expand></th></expand></th></expand> | <expand t<="" th=""><th><expand s<="" th="" to=""><th>AVX</th><th>Square Roo</th><th>ts; Inserts; Extracts;</th><th>Masked Sto</th></expand></th></expand> | <expand s<="" th="" to=""><th>AVX</th><th>Square Roo</th><th>ts; Inserts; Extracts;</th><th>Masked Sto</th></expand> | AVX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Square Roo                | ts; Inserts; Extracts;   | Masked Sto   |

| 🕬 🚺 [loop at nbody.cc:57 in main]       | 1,810s 📼                                           | 1,810s 📼            |                  |        | Vectorized (Body)                                                                                                                                                                                        |                                                                                                                                                            | 2,00                                                                                                                 | AVX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Square Root               | s; Inserts; Extracts; Ma | isked Stores |

| i>[loop at nbody.cc:57 in main]         | 0,010s l                                           | 0,010s l            |                  |        | Peeled                                                                                                                                                                                                   |                                                                                                                                                            |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |                          |              |

| >[loop at nbody.cc:54 in main]          | 0,000s I                                           | 1,820s 🚍            |                  |        | Scalar                                                                                                                                                                                                   | inner loop                                                                                                                                                 |                                                                                                                      | AVX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Shuffles; Ins             | erts; Extracts           |              |

| >[loop at nbody.cc:54 in main]          | 0,000s1                                            | 1,820s 🚍            |                  |        | Scalar                                                                                                                                                                                                   | inner loop                                                                                                                                                 |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |                          |              |

| < [                                     |                                                    |                     | 5. <del></del> 5 |        |                                                                                                                                                                                                          | 111                                                                                                                                                        |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |                          |              |

| Top Down Source Loop Assemi             | bly Assistance                                     | e Recommer          | dations          | Comp   | iler Diagnostic Details                                                                                                                                                                                  |                                                                                                                                                            |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |                          |              |

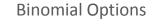

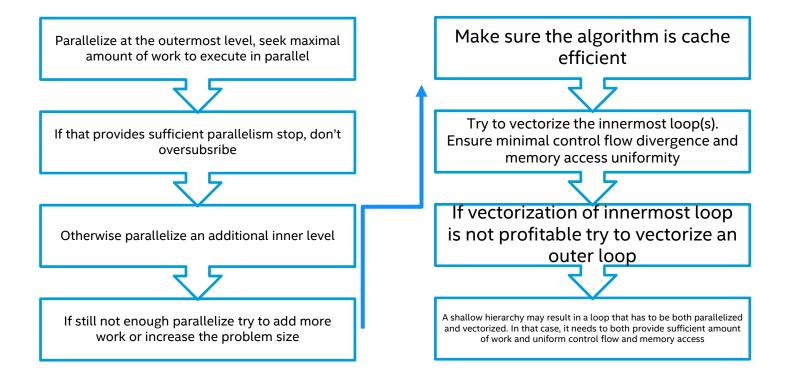

| File: nbody.cc:57 main                  |                                                    |                     |                  |        |                                                                                                                                                                                                          |                                                                                                                                                            |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |                          |              |