# Practical Data Compression for Modern Memory Hierarchies

Gennady G. Pekhimenko

CMU-CS-16-116 July 2016

Computer Science Department School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

#### **Thesis Committee:**

Todd C. Mowry, Co-Chair

Onur Mutlu, Co-Chair

Kayvon Fatahalian

David A. Wood, University of Wisconsin-Madison

Douglas C. Burger, Microsoft

Michael A. Kozuch, Intel

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Copyright © 2016 Gennady G. Pekhimenko

This research was sponsored by the National Science Foundation under grant numbers CNS-0720790, CCF-0953246, CCF-1116898, CNS-1423172, CCF-1212962, CNS-1320531, CCF-1147397, and CNS- 1409723, the Defense Advanced Research Projects Agency, the Semiconductor Research Corporation, the Gigascale Systems Research Center, Intel URO Memory Hierarchy Program, Intel ISTC-CC, and gifts from AMD, Google, IBM, Intel, Nvidia, Oracle, Qualcomm, Samsung, and VMware. We also acknowledge the support through PhD fellowships from Nvidia, Microsoft, Qualcomm, and NSERC.

The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of any sponsoring institution, the U.S. government or any other entity.

## **Abstract**

Although compression has been widely used for decades to reduce file sizes (thereby conserving storage capacity and network bandwidth when transferring files), there has been limited use of hardware-based compression within modern memory hierarchies of commodity systems. Why not? Especially as programs become increasingly data-intensive, the capacity and bandwidth within the memory hierarchy (including caches, main memory, and their associated interconnects) have already become increasingly important bottlenecks. If hardware-based data compression could be applied successfully to the memory hierarchy, it could potentially relieve pressure on these bottlenecks by increasing effective capacity, increasing effective bandwidth, and even reducing energy consumption.

In this thesis, we describe a new, practical approach to integrating hardware-based data compression within the memory hierarchy, including on-chip caches, main memory, and both on-chip and off-chip interconnects. This new approach is fast, simple, and effective in saving storage space. A key insight in our approach is that access time (including decompression latency) is critical in modern memory hierarchies. By combining inexpensive hardware support with modest OS support, our holistic approach to compression achieves substantial improvements in performance and energy efficiency across the memory hierarchy. Using this new approach, we make several major contributions in this thesis.

First, we propose a new compression algorithm, *Base-Delta-Immediate Compression*  $(B\Delta I)$ , that achieves high compression ratio with very low compression/decompression latency.  $B\Delta I$  exploits the existing low dynamic range of values present in many cache lines to compress them to smaller sizes using Base+Delta encoding.

Second, we observe that the compressed size of a cache block can be indicative of its reuse. We use this observation to develop a new cache insertion policy for compressed caches, the *Size-based Insertion Policy (SIP)*, which uses the size of a compressed block as one of the metrics to predict its potential future reuse.

Third, we propose a new main memory compression framework, *Linearly Compressed Pages (LCP)*, that significantly reduces the complexity and power cost of supporting main

memory compression. We demonstrate that *any* compression algorithm can be adapted to fit the requirements of LCP, and that LCP can be efficiently integrated with the existing cache compression designs, avoiding extra compression/decompression.

Finally, in addition to exploring compression-related issues and enabling practical solutions in modern CPU systems, we discover new problems in realizing hardware-based compression for GPU-based systems and develop new solutions to solve these problems.

# **Acknowledgments**

First of all, I would like to thank my advisers, Todd Mowry and Onur Mutlu, for always trusting me in my research experiments, giving me enough resources and opportunities to improve my work, as well as my presentation and writing skills.

I am grateful to Michael Kozuch and Phillip Gibbons for being both my mentors and collaborators. I am grateful to the members of my PhD committee: Kayvon Fatahalian, David Wood, and Doug Burger for their valuable feedback and for making the final steps towards my PhD very smooth. I am grateful to Deb Cavlovich who allowed me to focus on my research by magically solving all other problems.

I am grateful to SAFARI group members that were more than just lab mates. Vivek Seshadri was always supportive for my crazy ideas and was willing to dedicate his time and energy to help me in my work. Chris Fallin was a rare example of pure smartness mixed with great work ethic, but still always had time for an interesting discussion. From Yoongu Kim I learned a lot about the importance of details, and hopefully I learned something from his aesthetic sense as well. Lavanya Subramanian was my fellow cubic mate who showed me an example on how to successfully mix work with personal life and how to be supportive for others. Justin Meza helped me to improve my presentation and writing skills in a very friendly manner (as everything else he does). Donghyuk Lee taught me everything I know about DRAM and was always an example of work dedication for me. Nandita Vijaykumar was my mentee, collaborator, and mentor all at the same time, but, most importantly, a friend that was always willing to help. Rachata Ausavarungnirun was our food guru and one of the most reliable and friendly people in the group. Hongyi Xin reminded me about everything I almost forgot from biology and history classes, and also taught me everything I know now in the amazing field of bioinformatics. Kevin Chang and Kevin Hsieh were always helpful and supportive when it matters most. Samira Khan was always available for a friendly chat when I really need it. Saugata Ghose was my rescue guy during our amazing trip to Prague. I also thank other members of the SAFARI group for their assistance and support: HanBin Yoon, Jamie Liu, Ben Jaiyen, Yixin Luo, Yang

#### Li, and Amirali Boroumand.

Michelle Goodstein, Olatunji Ruwase and Evangelos Vlachos, senior PhD students, shared their experience and provided a lot of feedback early in my career. I am grateful to Tyler Huberty and Rui Cai for contributing a lot to my research and for being excellent undergraduate/masters researchers who selected me as a mentor from all the other options they had.

During my time at Carnegie Mellon, I met a lot of wonderful people: Michael Papamichael, Gabe Weisz, Alexey Tumanov, Danai Koutra and many others who helped and supported me in many different ways. I am also grateful to people at PDL and CALCM groups for accepting me in their communities.

I am grateful to my internship mentors for making my work in their companies mutually successful for both sides. At Microsoft Research, I had the privilege to closely work with Karin Strauss, Dimitrios Lymberopoulos, Oriana Riva, Ella Bounimova, Patrice Godefroid, and David Molnar. At NVIDIA Research, I had the privilege to closely work with Evgeny Bolotin, Steve Keckler, and Mike O'Connor. I am also grateful to my amazing collaborators from Georgia Tech: Hadi Esmaeilzadeh, Amir Yazdanbaksh, and Bradley Thwaites.

And last, but not least, I would like to acknowledge the enormous love and support that I received from my family: my wife Daria and our daughter Alyssa, my parents: Gennady and Larissa, and my brother Evgeny.

# **Contents**

|   | Abs  | tract   |                                                                                 | iii |

|---|------|---------|---------------------------------------------------------------------------------|-----|

|   | Ack  | nowled  | gments                                                                          | v   |

| 1 | Intr | oductio | on                                                                              | 1   |

|   | 1.1  | Focus   | of This Dissertation: Efficiency of the Memory Hierarchy                        | 1   |

|   |      | 1.1.1   | A Compelling Possibility: Compressing Data throughout the Full Memory Hierarchy | 2   |

|   |      | 1.1.2   | Why Traditional Data Compression Is Ineffective for Modern Memory Systems       | 3   |

|   | 1.2  | Relate  | d Work                                                                          | 3   |

|   |      | 1.2.1   | 3D-Stacked DRAM Architectures                                                   | 4   |

|   |      | 1.2.2   | In-Memory Computing                                                             | 4   |

|   |      | 1.2.3   | Improving DRAM Performance                                                      | 4   |

|   |      | 1.2.4   | Fine-grain Memory Organization and Deduplication                                | 5   |

|   |      | 1.2.5   | Data Compression for Graphics                                                   | 5   |

|   |      | 1.2.6   | Software-based Data Compression                                                 | 5   |

|   |      | 1.2.7   | Code Compression                                                                | 6   |

|   |      | 1.2.8   | Hardware-based Data Compression                                                 | 6   |

|   | 1.3  |         | S Statement: Fast and Simple Compression shout the Memory Hierarchy             | 6   |

|   | 1.4  | Contri  | butions                                                                         | 7   |

| 2 | Key  | y Challenges for Hardware-Based Memory Comp                 | ression              | 9  |

|---|------|-------------------------------------------------------------|----------------------|----|

|   | 2.1  | Compression and Decompression Latency                       |                      | 9  |

|   |      | 2.1.1 Cache Compression                                     |                      | 9  |

|   |      | 2.1.2 Main Memory                                           |                      | 10 |

|   |      | 2.1.3 On-Chip/Off-chip Buses                                |                      | 10 |

|   | 2.2  | Quickly Locating Compressed Data                            |                      | 10 |

|   | 2.3  | Fragmentation                                               |                      | 11 |

|   | 2.4  | Supporting Variable Size after Compression                  |                      | 12 |

|   | 2.5  | Data Changes after Compression                              |                      | 12 |

|   | 2.6  | Summary of Our Proposal                                     |                      | 13 |

| 3 | Base | se-Delta-Immediate Compression                              |                      | 15 |

|   | 3.1  | Introduction                                                |                      | 15 |

|   |      | 3.1.1 Our Approach: $B\Delta I$ Compression                 |                      | 16 |

|   | 3.2  | Background and Motivation                                   |                      | 17 |

|   | 3.3  | Base + Delta Encoding: Basic Idea                           |                      | 20 |

|   |      | 3.3.1 Why Does $B+\Delta$ Work?                             |                      | 21 |

|   |      | 3.3.2 Compression Algorithm                                 |                      | 22 |

|   |      | 3.3.3 Decompression Algorithm                               |                      | 24 |

|   | 3.4  | $B\Delta I$ Compression                                     |                      | 24 |

|   |      | 3.4.1 Why Could Multiple Bases Help?                        |                      | 24 |

|   |      | 3.4.2 B $\Delta$ I: Refining B+ $\Delta$ with Two Bases and | Minimal Complexity . | 26 |

|   | 3.5  | $B\Delta I$ : Design and Operation                          |                      | 28 |

|   |      | 3.5.1 Design                                                |                      | 28 |

|   |      | 3.5.2 Operation                                             |                      | 33 |

|   | 3.6  | Related Work                                                |                      | 33 |

|   |      | 3.6.1 Zero-based Designs                                    |                      | 34 |

|   |      | 3.6.2 Frequent Value Compression                            |                      | 34 |

|   |      | 3.6.3 Pattern-Based Compression Techniques .                |                      | 35 |

|   |     | 3.6.4    | Follow-up Work                          | 36 |

|---|-----|----------|-----------------------------------------|----|

|   | 3.7 | Evalua   | ation Methodology                       | 36 |

|   | 3.8 | Result   | s & Analysis                            | 38 |

|   |     | 3.8.1    | Single-core Results                     | 38 |

|   |     | 3.8.2    | Multi-core Results                      | 39 |

|   |     | 3.8.3    | Effect on Cache Capacity                | 41 |

|   |     | 3.8.4    | Effect on Bandwidth                     | 43 |

|   |     | 3.8.5    | Detailed Comparison with Prior Work     | 43 |

|   | 3.9 | Summ     | ary                                     | 45 |

| 4 | Con | npressio | on-Aware Cache Management               | 47 |

|   | 4.1 | Introd   | uction                                  | 47 |

|   | 4.2 | Motiva   | ating Observations                      | 50 |

|   |     | 4.2.1    | Size Matters                            | 50 |

|   |     | 4.2.2    | Size Varies                             | 51 |

|   |     | 4.2.3    | Size Can Indicate Reuse                 | 52 |

|   | 4.3 | CAMI     | P: Design and Implementation            | 55 |

|   |     | 4.3.1    | Background                              | 56 |

|   |     | 4.3.2    | Minimal-Value Eviction (MVE)            | 57 |

|   |     | 4.3.3    | Size-based Insertion Policy (SIP)       | 58 |

|   |     | 4.3.4    | CAMP for the V-Way Cache                | 60 |

|   |     | 4.3.5    | Overhead and Complexity Analysis        | 64 |

|   | 4.4 | Qualit   | ative Comparison with Prior Work        | 64 |

|   |     | 4.4.1    | Size-Aware Management in On-Chip Caches | 64 |

|   |     | 4.4.2    | Size-Aware Management in Web Caches     | 65 |

|   | 4.5 | Metho    | dology                                  | 66 |

|   |     | 4.5.1    | Evaluation Metrics                      | 66 |

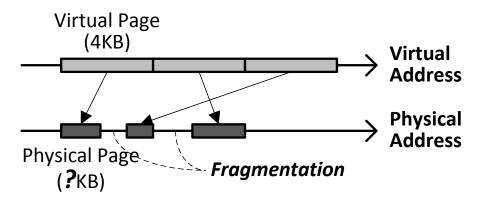

|   |     | 4.5.2    | Energy                                  | 67 |

|   |     | 453      | Parameters of Evaluated Schemes         | 67 |

|   | 4.6 | Result  | s and Analysis                             | 68  |

|---|-----|---------|--------------------------------------------|-----|

|   |     | 4.6.1   | Single-core Results                        | 68  |

|   |     | 4.6.2   | Multi-core Results                         | 73  |

|   |     | 4.6.3   | Sensitivity to the Compression Algorithm   | 75  |

|   |     | 4.6.4   | SIP with Uncompressed Cache                | 75  |

|   | 4.7 | Summ    | ary                                        | 76  |

| 5 | Mai | n Memo  | ory Compression: Linearly Compressed Pages | 77  |

|   | 5.1 | Introdu | uction                                     | 77  |

|   |     | 5.1.1   | Shortcomings of Prior Approaches           | 78  |

|   |     | 5.1.2   | Our Approach: Linearly Compressed Pages    | 79  |

|   | 5.2 | Backg   | round on Main Memory Compression           | 81  |

|   |     | 5.2.1   | Compressing In-Memory Data                 | 81  |

|   |     | 5.2.2   | Challenges in Memory Compression           | 82  |

|   |     | 5.2.3   | Prior Work on Memory Compression           | 83  |

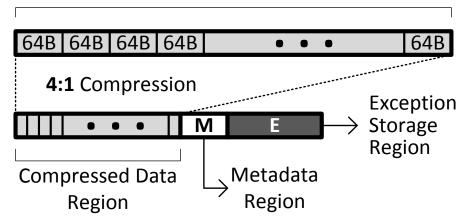

|   | 5.3 | Linear  | ly Compressed Pages                        | 85  |

|   |     | 5.3.1   | LCP: Basic Idea                            | 85  |

|   |     | 5.3.2   | LCP Operation                              | 87  |

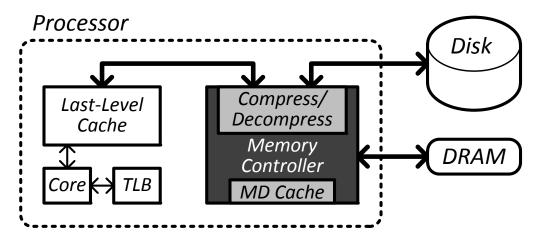

|   | 5.4 | Detaile | ed Design                                  | 89  |

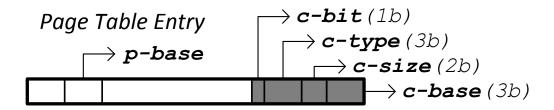

|   |     | 5.4.1   | Page Table Entry Extension                 | 89  |

|   |     | 5.4.2   | LCP Organization                           | 90  |

|   |     | 5.4.3   | Operating System Memory Management         | 93  |

|   |     | 5.4.4   | Changes to the Cache Tagging Logic         | 93  |

|   |     | 5.4.5   | Changes to the Memory Controller           | 93  |

|   |     | 5.4.6   | Handling Page Overflows                    | 95  |

|   |     | 5.4.7   | Compression Algorithms                     | 97  |

|   | 5.5 | LCP C   | Optimizations                              | 98  |

|   |     | 5.5.1   | Enabling Memory Bandwidth Reduction        | 99  |

|   |     | 5.5.2   | Zero Pages and Zero Cache Lines            | 100 |

|   | 5.6 | Metho   | dology                                              | 100 |

|---|-----|---------|-----------------------------------------------------|-----|

|   | 5.7 | Result  | s                                                   | 101 |

|   |     | 5.7.1   | Effect on DRAM Capacity                             | 101 |

|   |     | 5.7.2   | Effect on Performance                               | 104 |

|   |     | 5.7.3   | Effect on Bus Bandwidth and Memory Subsystem Energy | 107 |

|   |     | 5.7.4   | Analysis of LCP Parameters                          | 109 |

|   |     | 5.7.5   | Comparison to Stride Prefetching                    | 110 |

|   | 5.8 | Summ    | ary                                                 | 111 |

| 6 | Tog | gle-Awa | are Bandwidth Compression                           | 113 |

|   | 6.1 | Introd  | uction                                              | 113 |

|   |     | 6.1.1   | Compression & Communication Energy                  | 114 |

|   |     | 6.1.2   | Toggle-Aware Compression                            | 115 |

|   | 6.2 | Backg   | round                                               | 116 |

|   | 6.3 | Motiva  | ation and Analysis                                  | 117 |

|   | 6.4 | Toggle  | e-aware Compression                                 | 121 |

|   |     | 6.4.1   | Energy vs. Performance Trade-off                    | 121 |

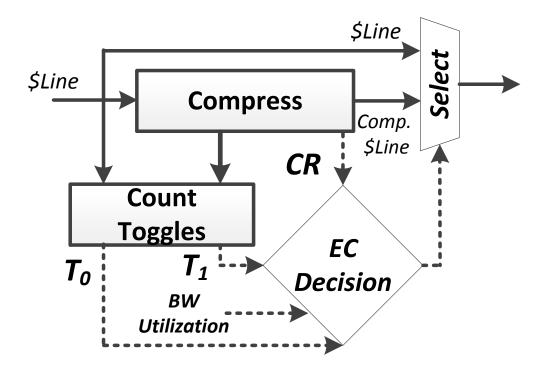

|   |     | 6.4.2   | Energy Control (EC)                                 | 123 |

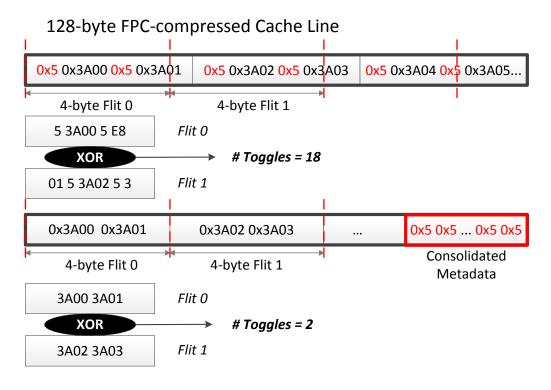

|   |     | 6.4.3   | Metadata Consolidation                              | 123 |

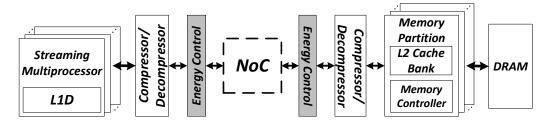

|   | 6.5 | EC Ar   | chitecture                                          | 125 |

|   |     | 6.5.1   | Toggle Computation for On-Chip Interconnect         | 126 |

|   |     | 6.5.2   | Toggle Computation for DRAM                         | 127 |

|   |     | 6.5.3   | EC and Data Bus Inversion                           | 127 |

|   |     | 6.5.4   | Complexity Estimation                               | 128 |

|   | 6.6 | Metho   | odology                                             | 129 |

|   | 6.7 | Evalua  | ation                                               | 129 |

|   |     | 6.7.1   | DRAM Bus Results                                    | 130 |

|   |     | 6.7.2   | On-Chip Interconnect Results                        | 135 |

|   |     | 6.7.3   | Effect of Metadata Consolidation                    | 138 |

|     | 6.8    | Related  | d Work                                     | 140 |

|-----|--------|----------|--------------------------------------------|-----|

|     | 6.9    | Summa    | ary                                        | 141 |

| 7   | Putti  | ing It A | ll Together                                | 143 |

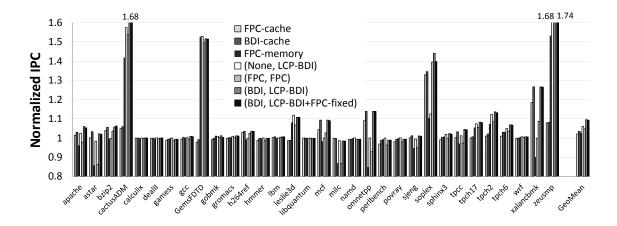

|     | 7.1    | Main N   | Memory + Cache Compression                 | 143 |

|     |        | 7.1.1    | Effect on Performance                      | 144 |

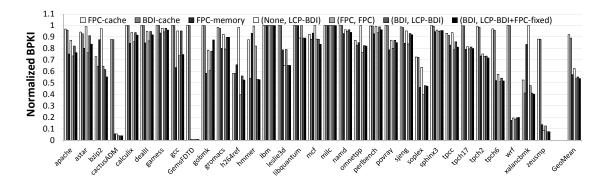

|     |        | 7.1.2    | Effect on Bus Bandwidth                    | 146 |

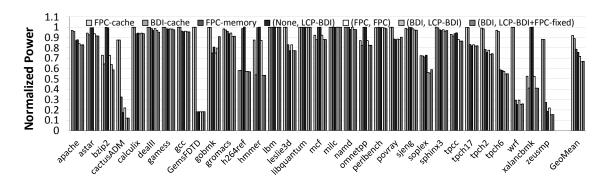

|     |        | 7.1.3    | Effect on Energy                           | 147 |

| 8   | Conc   | clusions | and Future Work                            | 149 |

|     | 8.1    | Future   | Work Directions                            | 150 |

|     |        | 8.1.1    | Compiler-Assisted Data Compression         | 150 |

|     |        | 8.1.2    | Data Compression for Non-Volatile Memories | 151 |

|     |        | 8.1.3    | New Efficient Representations for Big Data | 151 |

| Bil | bliogr | aphv     |                                            | 155 |

# **List of Figures**

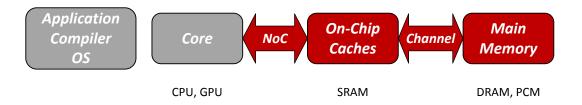

| 1.1  | Data compression from the core to the main memory                                                                                                                                                                                                                            | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

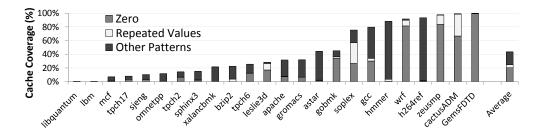

| 3.1  | Percentage of cache lines with different data patterns in a 2MB L2 cache. "Other Patterns" includes "Narrow Values"                                                                                                                                                          | 19 |

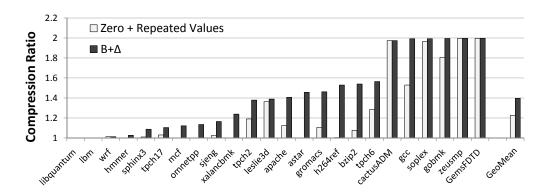

| 3.2  | Effective compression ratio with different value patterns                                                                                                                                                                                                                    | 21 |

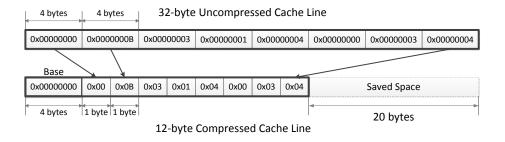

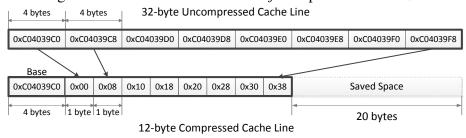

| 3.3  | Cache line from $h264ref$ compressed with $B+\Delta$                                                                                                                                                                                                                         | 22 |

| 3.4  | Cache line from $perlbench$ compressed with $B+\Delta$                                                                                                                                                                                                                       | 22 |

| 3.5  | Cache line from $mcf$ compressed by $B+\Delta$ (two bases)                                                                                                                                                                                                                   | 25 |

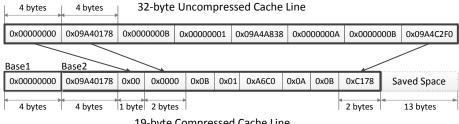

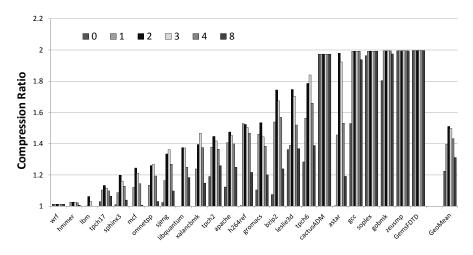

| 3.6  | Effective compression ratio with different number of bases. "0" corresponds to zero and repeated value compression                                                                                                                                                           | 25 |

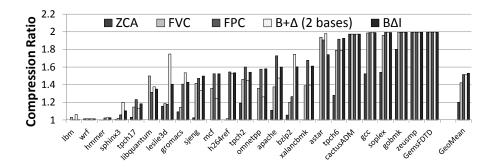

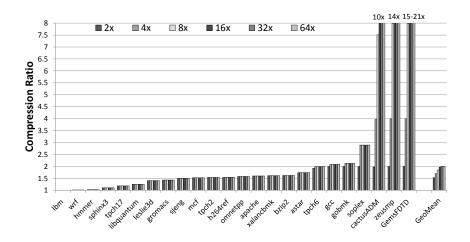

| 3.7  | Compression ratio comparison of different algorithms: ZCA [54], FVC [256], FPC [10], $B+\Delta$ (two arbitrary bases), and $B\Delta I$ . Results are obtained on a cache with twice the tags to accommodate more cache lines in the same data space as an uncompressed cache | 27 |

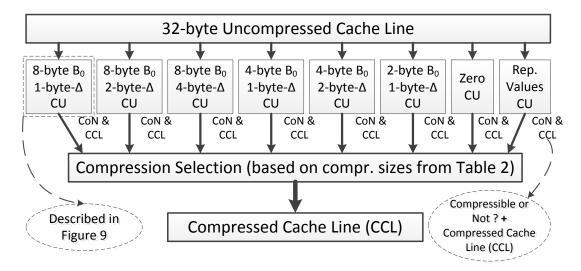

| 3.8  | Compressor design. CU: Compressor unit                                                                                                                                                                                                                                       | 28 |

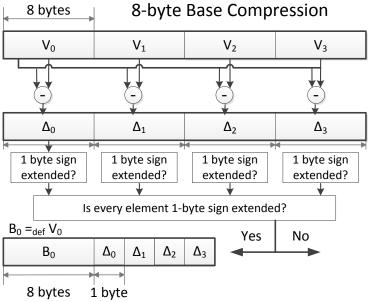

| 3.9  | Compressor unit for 8-byte base, 1-byte $\Delta$                                                                                                                                                                                                                             | 30 |

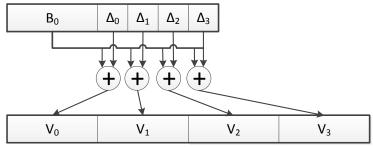

| 3.10 | Decompressor design                                                                                                                                                                                                                                                          | 30 |

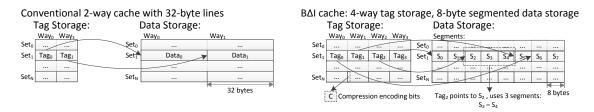

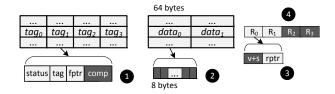

| 3.11 | $B\Delta I$ vs. conventional cache organization. Number of tags is doubled, compression encoding bits are added to every tag, data storage is the same in size, but partitioned into segments                                                                                | 31 |

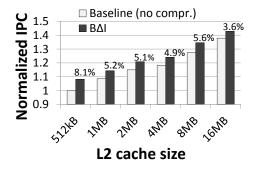

| 3.12 | (a) IPC                                                                                                                                                                                                                                                                      | 39 |

| 3.13 | (b) MPKI                                                                                                                                                                                                                                                                     | 39 |

| 3.14 | Performance of $B\Delta I$ with different cache sizes. Percentages show improvement over the baseline cache (same size)                                                                                                                                                      | 39 |

|      |                                                                                                                                                                                                                                                                              |    |

| 3.15 | show improvement over the baseline uncompressed cache                                                                                                                                                                                                                                                                       | 40 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

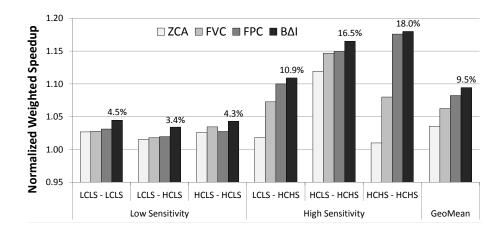

| 3.16 | IPC comparison of $B\Delta I$ against lower and upper limits in performance (from 512kB 2-way - 4MB 16-way L2 cache). Percentages on the GeoMean bars show how close $B\Delta I$ gets to the performance of the cache with twice the size (upper limit)                                                                     | 42 |

| 3.17 | Effective compression ratio vs. number of tags                                                                                                                                                                                                                                                                              | 43 |

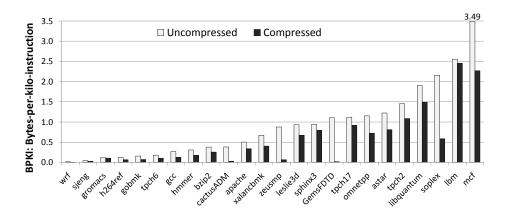

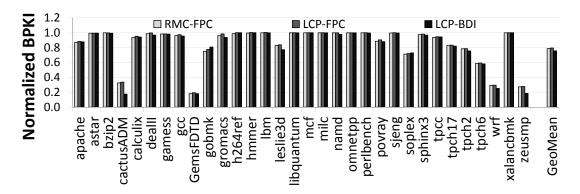

| 3.18 | Effect of compression on bus bandwidth (in terms of BPKI) between L2 (256kB) and L3 (8MB)                                                                                                                                                                                                                                   | 44 |

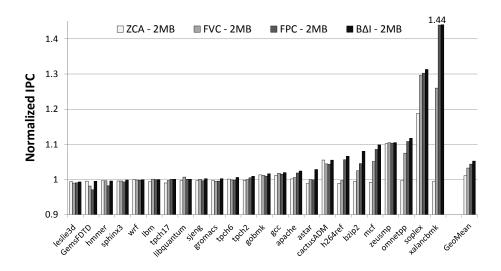

| 3.19 | Performance of $B\Delta I$ vs. prior work for a 2MB L2 cache                                                                                                                                                                                                                                                                | 44 |

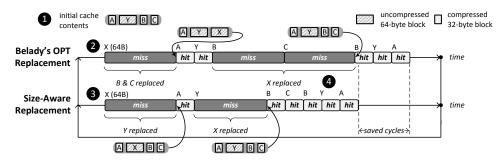

| 4.1  | Example demonstrating downside of not including block size information in replacement decisions                                                                                                                                                                                                                             | 49 |

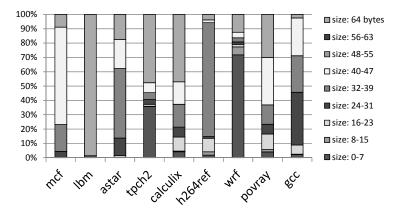

| 4.2  | Compressed block size distribution for representative applications with the BDI [185] compression algorithm                                                                                                                                                                                                                 | 51 |

| 4.3  | Code example: size and reuse distance relationship                                                                                                                                                                                                                                                                          | 53 |

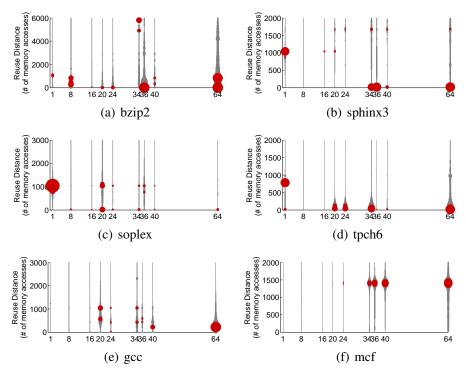

| 4.4  | Plots demonstrate the relationship between the compressed block size and reuse distance. Dark red circles correspond to the most frequent reuse distances for every size. The first five workloads ((a)–(e)) have some relation between size and reuse, while the last one (f) do not show that size is indicative of reuse | 54 |

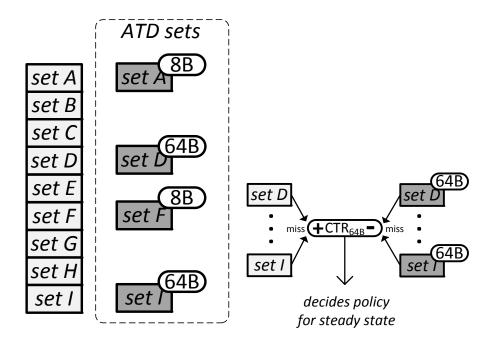

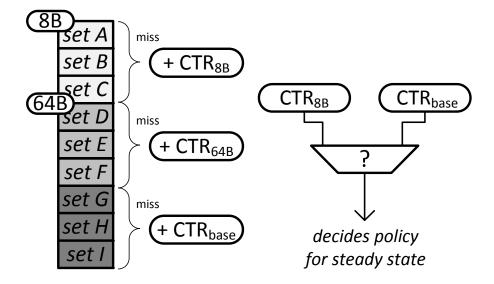

| 4.5  | Set selection during training and decision of best insertion policy based on difference in miss rate in MTD/ATD                                                                                                                                                                                                             | 59 |

| 4.6  | V-Way + compression cache design                                                                                                                                                                                                                                                                                            | 61 |

| 4.7  | Set selection during training and update of counters on misses to each region.                                                                                                                                                                                                                                              | 63 |

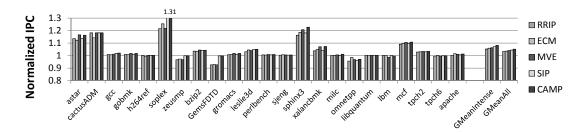

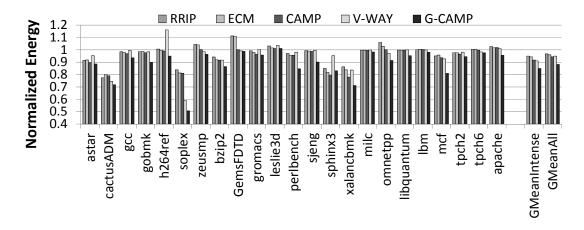

| 4.8  | Performance of our local replacement policies vs. RRIP and ECM, normalized to LRU                                                                                                                                                                                                                                           | 68 |

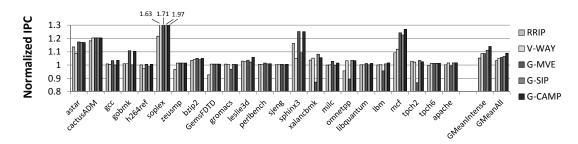

| 4.9  | Performance of our global replacement policies vs. RRIP and V-Way, normalized to LRU                                                                                                                                                                                                                                        | 68 |

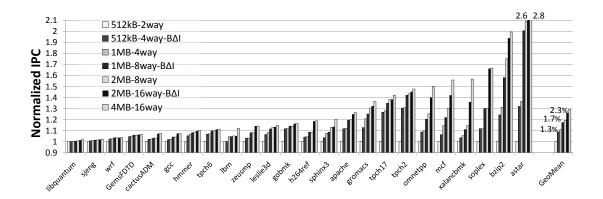

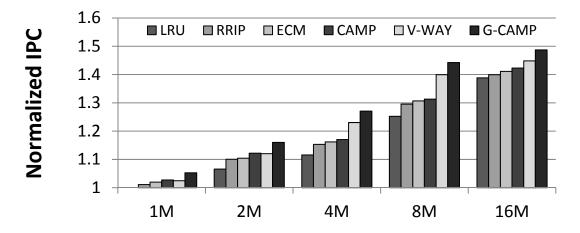

| 4.10 | Performance with 1M – 16MB L2 caches                                                                                                                                                                                                                                                                                        | 70 |

| 4.11 | Effect on memory subsystem energy                                                                                                                                                                                                                                                                                           | 71 |

| 4 12 | Effect on compression ratio with a 2MB L2 cache                                                                                                                                                                                                                                                                             | 73 |

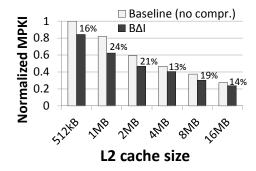

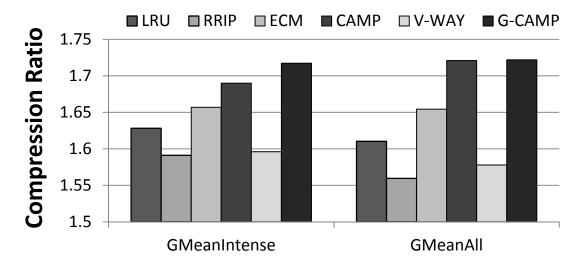

| 4.13 | Normalized weighted speedup, 2-cores with 2MB L2                                                                        | 74  |

|------|-------------------------------------------------------------------------------------------------------------------------|-----|

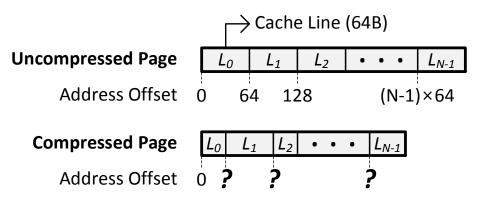

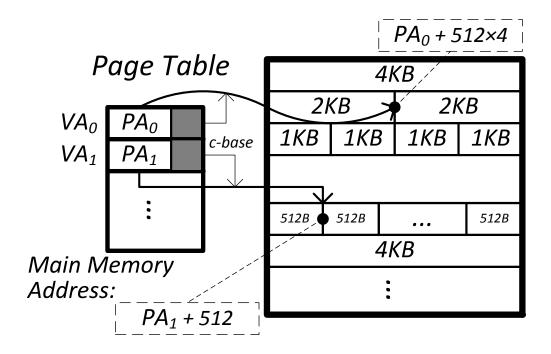

| 5.1  | Main Memory Page Mapping Challenge                                                                                      | 82  |

| 5.2  | Cache Line Address Computation Challenge                                                                                | 83  |

| 5.3  | Organization of a Linearly Compressed Page                                                                              | 86  |

| 5.4  | Memory request flow                                                                                                     | 87  |

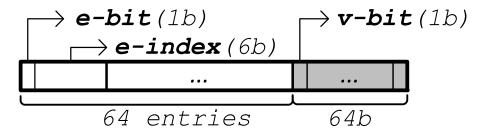

| 5.5  | Page table entry extension                                                                                              | 89  |

| 5.6  | Physical memory layout with the LCP framework                                                                           | 91  |

| 5.7  | Metadata region, when $n=64.\ldots\ldots\ldots\ldots$                                                                   | 92  |

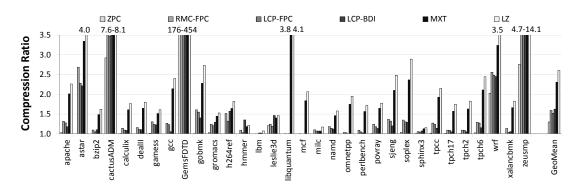

| 5.8  | Main memory compression ratio                                                                                           | 102 |

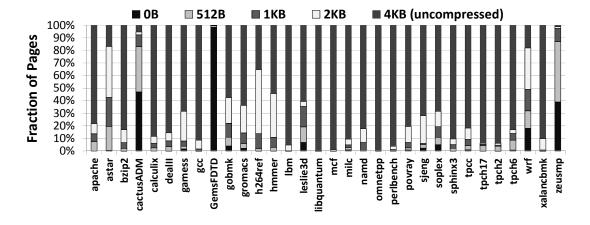

| 5.9  | Compressed page size distribution with LCP-BDI                                                                          | 103 |

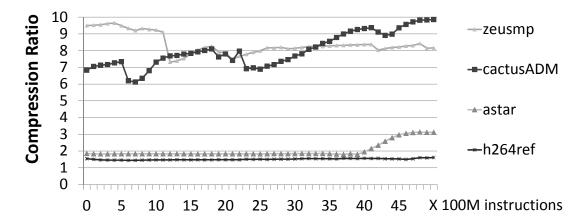

| 5.10 | Compression ratio over time with LCP-BDI                                                                                | 104 |

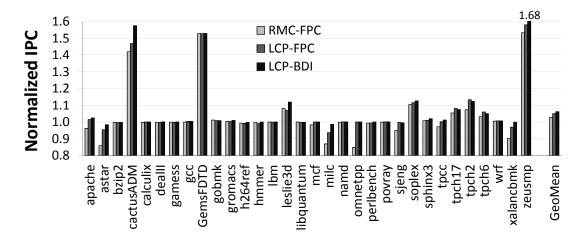

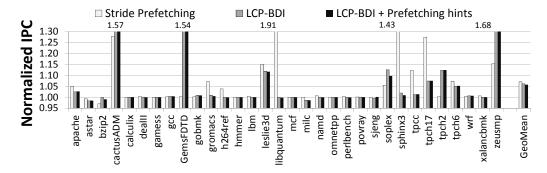

| 5.11 | Performance comparison (IPC) of different compressed designs for the single-core system                                 | 105 |

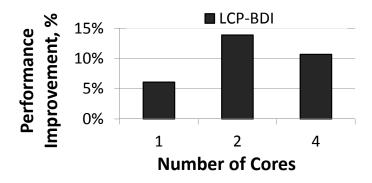

| 5.12 | Average performance improvement (weighted speedup)                                                                      | 106 |

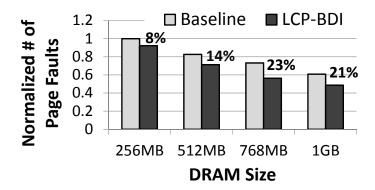

| 5.13 | Number of page faults (normalized to Baseline with 256MB)                                                               | 106 |

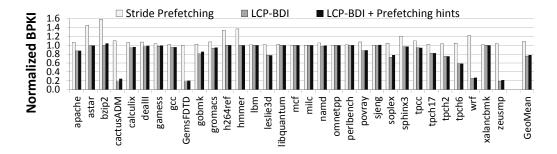

| 5.14 | Effect of different main memory compression schemes on memory bandwidth                                                 | 108 |

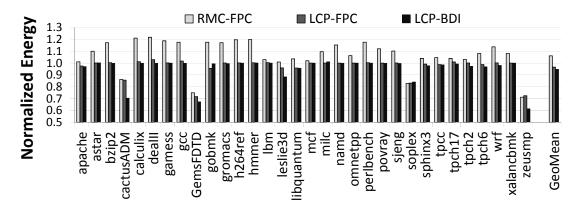

| 5.15 | Effect of different main memory compression schemes on memory subsystem energy                                          | 108 |

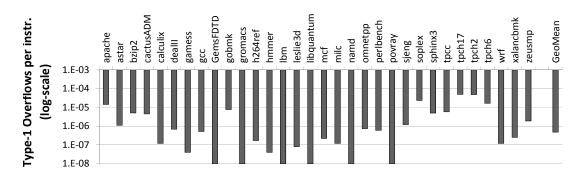

| 5.16 | Type-1 page overflows for different applications                                                                        | 109 |

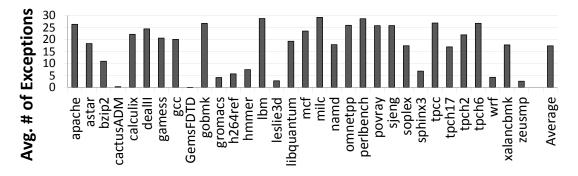

| 5.17 | Average number of exceptions per compressed page for different applications                                             | 110 |

| 5.18 | Performance comparison with stride prefetching, and using prefetcher hints with the LCP-framework                       | 111 |

| 5.19 | Bandwidth comparison with stride prefetching                                                                            | 112 |

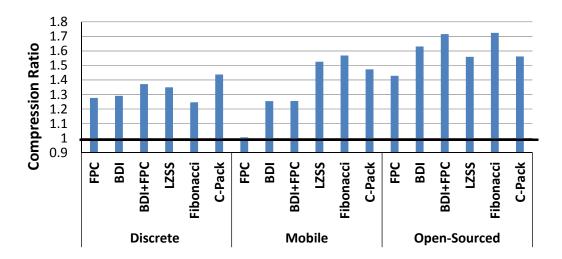

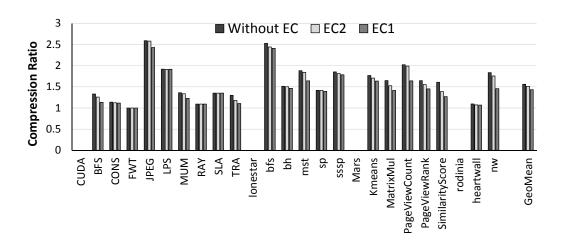

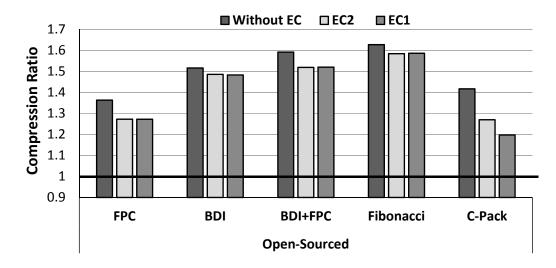

| 6.1  | Effective bandwidth compression ratios for various GPU applications and compression algorithms (higher bars are better) | 118 |

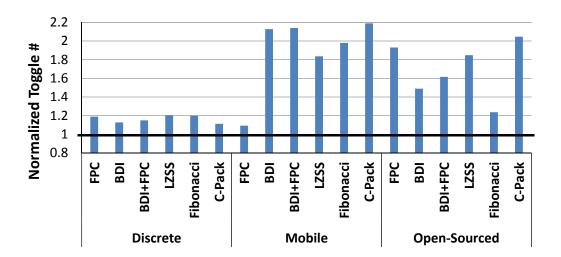

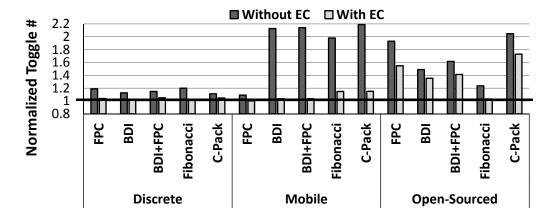

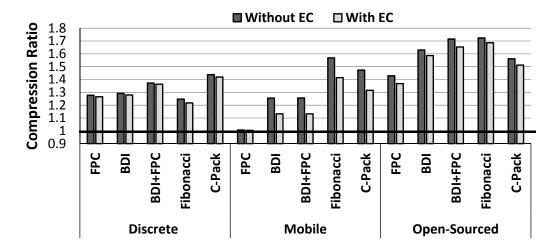

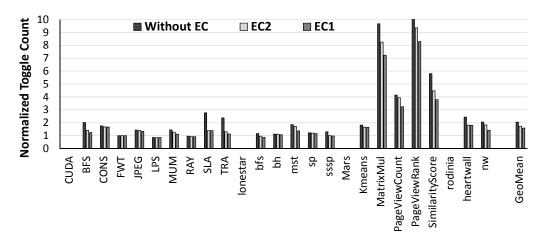

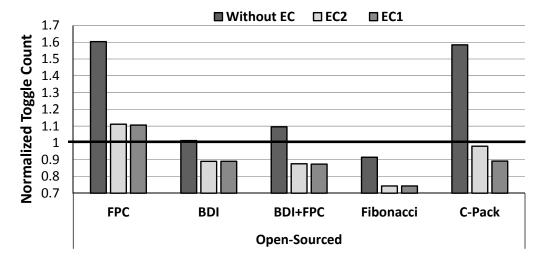

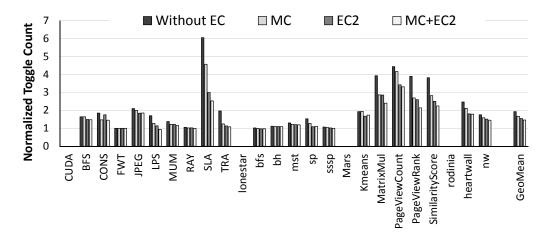

| 6.2  | Bit toggle count increase due to compression                                                                            | 120 |

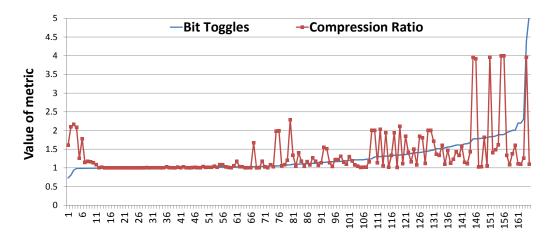

| 6.3  | Normalized bit toggle count vs. compression ratio (with the FPC algorithm) for each of the discrete GPU applications | 121 |

|------|----------------------------------------------------------------------------------------------------------------------|-----|

| 6.4  | Bit toggles without compression                                                                                      | 122 |

| 6.5  | Bit toggles after compression.                                                                                       | 122 |

| 6.6  | Energy Control decision mechanism                                                                                    | 124 |

| 6.7  | Bit toggle count w/o and with Metadata Consolidation                                                                 | 125 |

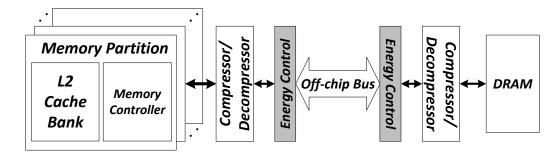

| 6.8  | System overview with interconnect compression and EC                                                                 | 126 |

| 6.9  | System overview with off-chip bus compression and EC                                                                 | 126 |

| 6.10 | Effect of Energy Control on the number of toggles on DRAM bus                                                        | 130 |

| 6.11 | Effective DRAM bandwidth increase for different applications                                                         | 131 |

| 6.12 | Effect of Energy Control with C-Pack compression algorithm on the number of DRAM toggles                             | 132 |

| 6.13 | Effective DRAM bandwidth increase with C-Pack algorithm                                                              | 132 |

| 6.14 | Speedup with C-Pack compression algorithm                                                                            | 134 |

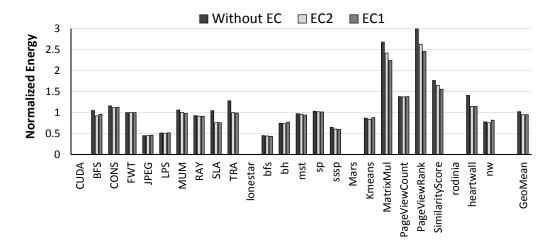

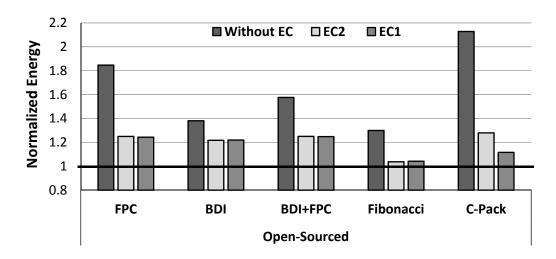

| 6.15 | Effect on the DRAM energy with C-Pack compression algorithm                                                          | 135 |

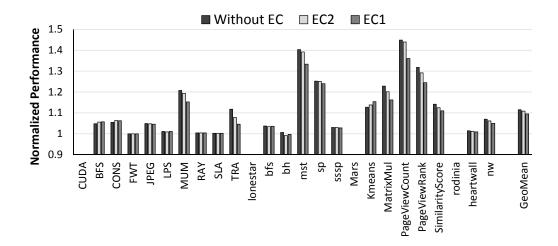

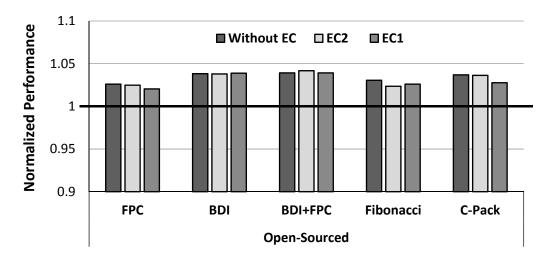

| 6.16 | Effect of Energy Control on the number of toggles in on-chip interconnect.                                           | 136 |

| 6.17 | Effect of Energy Control on compression ratio in on-chip interconnect                                                | 136 |

| 6.18 | Effect of Energy Control on performance when compression is applied to on-chip interconnect                          | 138 |

| 6.19 | Effect of Energy Control on on-chip interconnect energy                                                              | 139 |

| 6.20 | Effect of Metadata Consolidation on DRAM bit toggle count with FPC compression algorithm                             | 139 |

| 7.1  | Performance comparison (IPC) of different compressed designs                                                         | 145 |

| 7.2  | Effect of cache and main memory compression on memory bandwidth                                                      | 146 |

| 7.3  | Effect of cache and main memory compression on DRAM bus energy                                                       | 147 |

# **List of Tables**

| 3.1 | Qualitative comparison of $B\Delta I$ with prior work. LDR: Low dynamic range. Bold font indicates desirable characteristics                                                                                                                                                                                                                                                                                                                      | 18 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | $B\Delta I$ encoding. All sizes are in bytes. Compressed sizes (in bytes) are given for 32-/64-byte cache lines                                                                                                                                                                                                                                                                                                                                   | 29 |

| 3.3 | Storage cost analysis for 2MB 16-way L2 cache, assuming 64-byte cache lines, 8-byte segments, and 36 bits for address space                                                                                                                                                                                                                                                                                                                       | 32 |

| 3.4 | Major parameters of the simulated system                                                                                                                                                                                                                                                                                                                                                                                                          | 36 |

| 3.5 | Cache hit latencies used in simulations (in cycles). $B\Delta I$ caches have +1 cycle for 0.5–4MB (+2 cycle for others) on a hit/miss due to larger tag stores, and +1 cycle for decompression                                                                                                                                                                                                                                                    | 37 |

| 3.6 | Benchmark characteristics and categories: <b>Comp. Ratio</b> (effective compression ratio for 2MB B $\Delta$ I L2) and <b>Sens.</b> (cache size sensitivity). Sensitivity is the ratio of improvement in performance by going from 512kB to 2MB L2 (L - low ( $\leq 1.10$ ), H - high ( $> 1.10$ )). For compression ratio: L - low ( $\leq 1.50$ ), H - high ( $> 1.50$ ). <b>Cat.</b> means category based on compression ratio and sensitivity | 38 |

| 3.7 | Average performance improvement of $B\Delta I$ over other mechanisms: No Compression, ZCA, FVC, and FPC                                                                                                                                                                                                                                                                                                                                           | 41 |

| 4.1 | Storage overhead of different mechanisms for a 2MB L2 cache. "V-Way+C" means V-Way with compression                                                                                                                                                                                                                                                                                                                                               | 64 |

| 4.2 | Major parameters of the simulated system                                                                                                                                                                                                                                                                                                                                                                                                          | 67 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 4.3                               | Performance (IPC) / Miss rate (MPKI) comparison between our cache management policies and prior works, 2MB L2 cache. All numbers are pairwise percentage improvements over the corresponding comparison points and averaged across fourteen memory-intensive applications 69 |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>5.1</li><li>5.2</li></ul> | Major Parameters of the Simulated Systems                                                                                                                                                                                                                                    |

| 6.1                               | Major Parameters of the Simulated Systems                                                                                                                                                                                                                                    |

| 7.1                               | List of evaluated designs                                                                                                                                                                                                                                                    |

# **Chapter 1**

## Introduction

The recent Big Data revolution has had a transformative effect on many areas of science and technology [169]. Indeed, a key factor that has made Cloud Computing attractive is the ability to perform computation near these massive data sets. As we look toward the future, where our ability to capture detailed data streams from our environment is only expected to increase, it seems clear that many important computations will operate on increasingly larger data set sizes.

Unfortunately, data-intensive computing creates significant challenges for system designers. In particular, the large volume and flow of data places significant stress on the capacity and bandwidth across the many layers that comprise modern *memory hierarchies*, thereby making it difficult to deliver high performance at low cost with minimal energy consumption.

# 1.1 Focus of This Dissertation: Efficiency of the Memory Hierarchy

This dissertation focuses on performance and energy efficiency of the modern memory hierarchies. We observe that existing systems have significant redundancy in the data (i) *stored* in the memory hierarchies (e.g., main memory, on-chip caches) and (ii) *transferred* across existing communication channels (e.g., off-chip bus and on-chip interconnect). Figure 1.1 shows parts of the system stack where we aim to apply data compression (in red/dark).

In this dissertation, we first propose a simple and fast yet efficient compression algo-

Figure 1.1: Data compression from the core to the main memory.

rithm that is suitable for on-chip cache compression. This algorithm solves one of the key challenges for cache compression: achieving low decompression latency, which is on the critical path of the execution. Then, we show that *compressed cache block size* is a new important factor when making cache replacement decisions that helps to outperform state-of-the-art cache replacement mechanisms.

We then propose a new design for main memory compression that solves a key challenge in realizing data compression in main memory: the disparity between how the data is stored (i.e., at a *page* granularity) and how it is accessed (i.e., at a *cache line* granularity).

Finally, we show that bandwidth compression—both on-chip and off-chip—can be efficient in providing high effective bandwidth in the context of modern GPUs (with more than a hundred real applications evaluated). At the same time, we find that there is a new important problem with bandwidth compression that makes it potentially energy inefficient – the significant increase in the number of *bit toggles* (i.e., the number of transitions between zeros and ones) that leads to an increase in dynamic energy. We provide an efficient solution to this problem.

# 1.1.1 A Compelling Possibility: Compressing Data throughout the Full Memory Hierarchy

At first glance, *data compression* may seem like an obvious approach to reducing the negative impacts of processing large amounts of data. In theory, if data compression could effectively reduce the size of the data without introducing significant overheads, it would relieve pressure on both the *capacity* of the various layers of the memory hierarchy (including caches, DRAM, non-volatile memory technologies, etc.) as well as the *bandwidth* of the communication channels (including memory buses, etc.) that transfer data between these layers. This in turn would allow system designers to avoid over-provisioning these resources, since they could deliver performance more efficiently as a function of system cost and/or power budget. Perhaps surprisingly, although forms of data compression have

been used for many years to reduce file system storage requirements (e.g., by using gzip to compress files), there has been little to no use of compression within modern memory hierarchies. Why not?

# 1.1.2 Why Traditional Data Compression Is Ineffective for Modern Memory Systems

Traditional file compression algorithms such as Lempel-Ziv [268] achieve high compression ratios by scanning through the file from the beginning, building up a dictionary of common character sequences (which is stored within the compressed file and used for decompression). In the context of storing files on disk, variations of Lempel-Ziv have been very popular because files are often accessed as sequential streams, and because the large decompression latencies are considered to be acceptable given that (i) disk accesses are already slow, and (ii) saving as much disk space as possible is typically a very high priority.

In contrast to accessing compressed files on disk, two things are fundamentally different when a processor accesses data (via loads and stores) within its memory hierarchy: (i) *latency* is extremely critical, and (ii) data is commonly *accessed randomly* (rather than sequentially). Because processor performance is so sensitive to memory access latency, it is critical that the *decompression latency* must be as small as possible when accessing compressed data within the memory hierarchy. Otherwise, system designers and users will quickly become disenchanted with memory compression if it costs them significant performance. Ideally, if decompression latency is small enough, compression within the memory hierarchy should actually *improve performance* by improving cache hit rates and reducing bandwidth-related stalls. The fact that main memory is randomly accessed creates additional challenges, including *locating* (as well as decompressing) arbitrary blocks of data efficiently, plus achieving significant compression ratios without being able to use Lempel-Ziv's approach of building up dictionaries over large access streams.

#### 1.2 Related Work

Several prior works have proposed different mechanisms to improve the efficiency of the memory hierarchy to provide (i) higher capacity, (ii) higher bandwidth, (iii) lower latency,

<sup>&</sup>lt;sup>1</sup>The only real exception that we are aware of is IBM's MXT technology [3], which was shipped in commercial products roughly 10 years ago, but which has not become widely adopted.

and (iv) higher energy efficiency. In this section, we summarize some of the approaches that are related to our work. We summarize those works based on their high-level insight and compare them with the mechanisms proposed in this thesis.

#### 1.2.1 3D-Stacked DRAM Architectures

One of the major limitations of the existing DRAM-based memories is their limited off-chip bandwidth. One way to overcome this limitation is by vertically stacking multiple DRAM chips that provide wider IO interfaces, and hence increase the available off-chip bandwidth to improve performance. Many recent works have proposed designs and architectures based on this idea (e.g., [101, 99, 99, 131, 84, 86]) to get higher off-chip bandwidth, or to utilize 3D-stacked memory's higher capacity as a cache (e.g., [28, 150, 151, 250]). These designs are largely orthogonal to the ideas proposed in this thesis, and hence can be used together.

#### 1.2.2 In-Memory Computing

Processing in memory (PIM) has been previously (e.g., [222, 215, 121, 69, 59, 174, 172, 110, 65]) and more recently (e.g., [207, 208, 206, 30, 82, 76, 175, 75, 144, 62]) explored to perform computation near the data to reduce the off-chip bandwidth bottleneck improving both the performance and energy efficiency. More recently the idea of PIM have been actively explored again in the context of 3D-stacked memory (e.g., [7, 8, 9, 19, 63, 67, 135, 228, 68, 81, 30, 175]). These prior works might require (i) programmer effort to map regular computation and data to PIM, or (ii) significant increase in the overall cost of the system and/or cost-per-bit of the modern DRAM. The mechanisms proposed in this dissertation are also applicable to systems that perform in-memory computation.

## **1.2.3** Improving DRAM Performance

Many prior works look at different ways to improve the efficiency of modern DRAM architectures by either reducing the average access latency (e.g., [134, 133, 207, 155, 35]) or enable higher parallelism within the DRAM itself (e.g., [120, 34]). The approaches used by these work include (i) exploiting DRAM heterogeneity (e.g., Tiered-Latency DRAM [134]), Dynamic Asymmetric Subarray [152], Low-Cost Interlinked Subarrays [33]), (ii) improving DRAM parallelism [120, 34], (iii) exploiting variation in DRAM latency (e.g., Adaptive Latency DRAM [133], ChargeCache [77]), (iv) smarter

refresh and scheduling mechanisms (e.g., [92, 147, 34, 191, 146, 240]), and (v) more intelligent memory scheduling and partitioning algorithms (e.g., [165, 164, 119, 118, 56, 129, 224, 238, 225, 226, 162, 44, 17, 128, 106, 18, 130, 167, 266]). Many of these techniques can significantly improve DRAM performance (in terms of latency and energy efficiency), but are not capable of providing higher effective off-chip bandwidth or higher effective DRAM capacity by exploiting the existing redundancy in the data itself. The ideas in this dissertation can be exploited in conjunction with many of these techniques, e.g., intelligent memory scheduling.

#### 1.2.4 Fine-grain Memory Organization and Deduplication

Several different proposals aim to improve memory performance by changing its page-granularity organization (e.g., fine-grain memory deduplication [40], fine-grain virtual page management [210]). The proposed frameworks usually require significant changes to the existing virtual page organization that frequently leads to a significant increase in the cost. The techniques proposed in this thesis are much less radical in the way they affect the higher levels of the systems stack. The key difference with the deduplication approach [40] is that data redundancy is exploited at a much finer granularity (e.g., 1–4 byte vs. 16–64 byte), hence much higher compression ratios are possible for many applications. Our techniques are complementary to fine-grain virtual page management works (e.g., [210]).

## 1.2.5 Data Compression for Graphics

Data compression is a widely used technique in the specialized area of texture compression [227, 2, 223] used in modern GPUs. These approaches have several major limitations. First, compressed textures are usually read-only that is not acceptable for many applications. Second, compression/decompression latency is quite significant that limits applicability of these algorithms to latency-insensitive applications. Our work is targeted towards more general-purpose workloads where it is difficult to customize the compression algorithm to very specialized characteristics found in graphics processing.

## 1.2.6 Software-based Data Compression

Several mechanisms were proposed to perform memory compression in software (e.g., in the compiler [124], in the operating system [246]) for various modern operating systems

(e.g., Linux [71], MacOS [14], Windows [66], AIX [90]). While these techniques can be quite efficient in reducing applications' memory footprint, their major limitation is very slow (usually software-based) decompression. This limits these mechanisms to compressing only "cold" pages (e.g., swap pages).

#### 1.2.7 Code Compression

Compression was successfully applied not only to the application data, but also to the code itself [122, 137, 42, 140, 41, 136, 139, 13, 252, 60, 247]. The primary goal in these works was usually to reduce the program footprint (especially in the context of embedded devices). The reduced footprint can allow for more instructions to be stored in the instruction caches, and hence reduce the number of instruction cache misses, which, in turn, improves performance. In this dissertation, we do not specialize for code compression. Instead, our goal is to enable general data compression. Hence, the key difference between these prior works on code compression with the designs proposed in this dissertation is in the compression algorithms themselves: code compression algorithms are usually significantly tuned for a specific input – instructions, and usually not effective for data compression.

#### 1.2.8 Hardware-based Data Compression

Hardware-based data compression received some attention in the past (e.g., [256, 3, 10, 45, 38, 57]), but unfortunately proposed general-purpose designs were not practical either due to unacceptable compression/decompression latency or high design complexity and high overhead to support variable size blocks after compression. In this thesis, we will show how to overcome these challenges in several practical designs across the whole memory hierarchy. We will provide comprehensive quantitative comparisons to multiple previous state-of-the-art works on hardware-based data compression (e.g., [10, 38, 53, 256, 57, 3]).

# 1.3 Thesis Statement: Fast and Simple Compression throughout the Memory Hierarchy

The key insight in our approach is that (i) *decompression latency* and (ii) *simplicity of design* are far more critical than *compression ratio* when designing a compression scheme that is effective for modern memory systems (in contrast to traditional file compression techniques aimed at disk storage). We have identified simple and effective mechanisms

for compressing data in on-chip caches (e.g., by exploiting *narrow dynamic ranges*) and in main memory (e.g., by adopting a common compression ratio for all cache blocks within a page) that achieve significant compression ratios (roughly a factor of two in most cases) while adding minimal access latency overhead [185, 183, 181, 177]. The simplicity of our proposed mechanisms enables elegant solutions for dealing with the practical challenges of how on-chip caches and main memories are organized in modern systems.

The ultimate goal of this research is to validate the following thesis:

It is possible to develop a new set of designs for data compression within modern memory hierarchies that are fast enough, simple enough, and effective enough in saving storage space and consumed bandwidth such that the resulting improvements in performance, cost, and energy efficiency will make such compression designs attractive to implement in future systems.

The hope is to achieve this goal through the following new mechanism:

Data compression hardware (along with appropriate operating system support) that (i) efficiently achieves significant compression ratios with negligible latencies for locating and decompressing data, and (ii) enables the seamless transfer of compressed data between all memory hierarchy layers.

As a result of this, future computer systems would be better suited to the increasingly data-intensive workloads of the future.

### 1.4 Contributions

This dissertation makes the following contributions.

- 1. We propose a new compression algorithm ( $B\Delta I$ ) that achieves a high compression ratio.  $B\Delta I$  exploits the existing low dynamic range of values present in many cache lines to compress them to smaller sizes using Base+Delta encoding.  $B\Delta I$  yields itself to a very low latency decompression pipeline (requiring only a masked vector addition). To our knowledge, no prior work achieved such low latency decompression at high compression ratio. **Chapter 3** describes  $B\Delta I$  implementation and its evaluation in more detail.

- 2. We observe that the compressed size of a cache block can be indicative of its reuse. We use this observation to develop a new cache insertion policy for compressed

caches, the Size-based Insertion Policy (SIP), which uses the size of a compressed block as one of the metrics to predict its potential future reuse. We introduce a new compressed cache replacement policy, Minimal-Value Eviction (MVE), which assigns a value to each cache block based on both its size and its reuse and replaces the set of blocks with the smallest value. Both policies are generally applicable to different compressed cache designs (both with local and global replacement) and can be used with different compression algorithms. **Chapter 4** describes our proposed design, Compression-Aware Management Policies (CAMP = MVE + SIP) in detail.

- 3. We propose a new compression framework (LCP) that solves the problem of efficiently computing the physical address of a compressed cache line in main memory with much lower complexity and power consumption than prior proposals. We demonstrate that *any* compression algorithm can be adapted to fit the requirements of LCP, and that LCP can be efficiently integrated with existing cache compression designs (**Chapter 7**), avoiding extra compression/decompression. **Chapter 5** provides detailed implementation and evaluation of this framework.

- 4. We observe that hardware-based bandwidth compression applied to on-chip/off-chip communication interfaces poses a new challenge for system designers: a potentially significant increase in the bit toggle count as a result of data compression. Without proper care, this increase can lead to significant energy overheads when transferring compressed data that was not accounted for in prior works. We propose a set of new mechanisms to address this new challenge: Energy Control and Metadata Consolidation. We provide a detailed analysis and evaluation of a large spectrum of GPU applications that justify (i) the usefulness of data compression for bandwidth compression in many real applications, (ii) as well as the existence of the bit toggle problem for bandwidth compression, and (iii) effectiveness of our new mechanisms to address bit toggle problem, in **Chapter 6**.

# Chapter 2

# **Key Challenges for Hardware-Based Memory Compression**

There are two major factors that limit the current use of data compression in modern memory hierarchies: (i) the increase in access latency due to compression/decompression and (ii) supporting variable data size after compression. In this chapter, we discuss these major factors and how they affect the possibility of applying data compression at different levels of the memory hierarchy.

## 2.1 Compression and Decompression Latency

## 2.1.1 Cache Compression

In order to make cache compression practical, we have to answer the following key question: what is the right compression algorithm for an on-chip memory hierarchy?

The conventional wisdom is usually to aim for the highest possible compression ratio. This is usually achieved by using existing software-based compression algorithms that work by finding common subsets of data and storing them only once (i.e., dictionary-based compression), and then simplifying these algorithms so that they can be implemented in hardware. Instead of following this conventional path, another option is to prioritize simplicity of the compression algorithm over its efficiency (i.e., compression ratio). In summary, the major challenge is to balance the compression/decompression *speed* (decompression latency is especially important, because it is on the execution critical path)

and *simplicity* (no complex or costly hardware changes), while still being *effective* (having good compression ratio) in saving storage space.

#### 2.1.2 Main Memory

For main memory, compression/decompression latency is still an important factor, but there is definitely more headroom to play with, since typical memory accesses can take hundreds of processor cycles. Similar to on-chip caches, decompression lays on the critical path of the execution, and hence is the top priority in selecting a proper compression algorithm. Prior attempts to use existing software-based algorithms (e.g., Lempel-Ziv [268]) were not successful [3], because even optimized versions of these algorithms for hardware had decompression latencies of 64 or more cycles.

#### 2.1.3 On-Chip/Off-chip Buses

Data compression is not only effective in providing higher capacity, it can also provide higher effective bandwidth when applied to communication channels. We call this effect bandwidth compression. For major memory communication channels (e.g., on-chip/off-chip buses), compression and decompression are usually equally important, since both of them are directly added to the data transfer latency: compression latency (before sending the data), and decompression latency (after the data is received). Hence, the challenge is to properly balance both of these latencies without sacrificing the compression ratio.

It is possible to avoid some of these overheads, by storing and transferring the data in compressed form. For example, if the main memory already stores compressed data, then there is no need to compress it again before transferring it to the on-chip caches, etc. In a holistic approach, where compression is applied across many layers of the memory hierarchy (e.g., on-chip caches and main memory), it is possible that there is almost no overhead for bandwidth compression since both the source and the destination can store data in the same compressed form.

## 2.2 Quickly Locating Compressed Data

While compression improves effective capacity and bandwidth, one challenge is due to the fact that it generates data blocks in variable sizes. It poses several challenges, and one of those challenges is the ability to quickly locate the compressed data. In the uncompressed

memory organization, finding a certain cache line within a memory page is usually trivial: cache line offset within a physical page is the same as the cache line offset within the virtual page. Unfortunately, compression adds yet another layer of indirection, where cache line offsets can vary significantly within a physical page, depending on compressed sizes of the previous cache lines on the same page.

For main memory, this means that we either need to store the offsets of all cache lines somewhere (either on-chip or in a different memory page) or continuously compute those offsets (multiple additions of the previous cache line sizes/offsets) from some metadata (which still needs to be stored somewhere). Both options can lead to (i) significant energy and latency overheads and (ii) can significantly complicate the final design [3]. It is important to mention that this challenge affects only main memory compression because of the disparity in how the data is stored (e.g., 4KB page granularity) and how it is accessed (e.g., 64B cache line granularity). This is usually not an issue for compressed cache organizations where tags and actual cache blocks utilize simple mapping algorithms. Similarly, it is not a problem for transferring compressed data over on-chip/off-chip communication channels, where data is usually transferred in small chunks (e.g., 16B flits in on-chip interconnects).

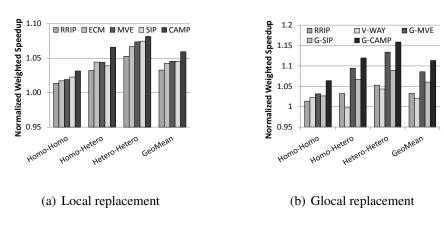

## 2.3 Fragmentation

Another challenge posed by the variable size blocks after compression is data fragmentation. For on-chip caches, the key issue is that after the compressed block is stored in the data store, it has a fixed size, and then it is immediately followed by another cache block (except for the last block). The problem arises when this compressed cache line is updated with new data. In that case, the cache line might not be compressed to the same size as it was before, and hence there is not enough space to simply store the new data for this cache block without moving data around. For a naïve compressed cache implementation, this could lead to significant energy waste and design complexity when shuffling data around after cache writebacks.

For main memory, there can be two types of fragmentation: page level and cache line level. Page level fragmentation happens due to the fact that it is hard to support a completely flexible page size after compression, because this would severely complicate the OS memory management process. Hence, in most realistic designs (e.g., [57]) only certain page sizes are possible (e.g., 1KB, 2KB and 4KB). This means that for every page that is not compressed to exactly one of these sizes, its physical size would be rounded up to the closest size that can fit this page. Cache line level fragmentation happens due to

the fact that many designs limit the number of compressed sizes for cache lines within a particular page to reduce the amount of metadata to track per cache line. Similar to page-level fragmentation, this means that many cache lines could be padded to align with the smallest acceptable compressed block size that fits them.

## 2.4 Supporting Variable Size after Compression

The variable-sized nature of compression output causes significant challenges for **on-chip/off-chip communication channels**. For example, off-chip DRAM buses are usually optimized to transfer one cache line (e.g., 64 bytes) at a time. There is no easy mechanism (without changes to the existing DRAM) to transfer smaller number of bytes faster. There are some exceptions with GPU-oriented memories (e.g., GDDR5 [88]) where cache lines are typically larger (128 bytes) and data buses are more narrow (32 bytes): hence every cache line is transferred in four pieces, and data compression with compression ratios up to  $4\times$  is possible without major changes to DRAM. On-chip interconnects usually transfer cache lines in several data chunks called flits. In this case, compression ratio also limited by the granularity of the flits.

## 2.5 Data Changes after Compression

Data compression inevitably changes the data itself, and, unfortunately, sometimes these changes can lead to significant energy overhead. There are several reasons for this. First, in every particular case, it actually matters whether a 0 or 1 is transferred or stored. For example, for the on-chip interconnect, that just transferred a 0 bit, transferring another 0 over the same pin that has just transferred a 0 is almost free in terms of energy, while transferring 1 would cost additional energy. Hence, higher number of switches on the interconnect wire (called bit toggles) negatively affects energy efficiency of data communication. Second, modern programming languages and compilers tend to store data in a regular fashion such that data is usually nicely aligned at a 4/8-byte granularity. This also nicely aligns with how the data is then transferred over communication channels (e.g., 16-byte alignment for many modern on-chip networks). This means that many similar bits are kept being transferred over the same pins, reducing the energy cost of data transfers. Unfortunately, data compression frequently breaks this unspoken assumption about "nice" data alignment, thereby significantly increasing the total number of bit toggles, and hence, increasing the energy of on-chip data transfers.

## 2.6 Summary of Our Proposal

In this dissertation, we aim to develop efficient solutions to overcome the described challenges.

To this end, we first propose a simple and fast yet efficient compression algorithm that is suitable for on-chip cache compression (**Chapter 3**). This algorithm solves one of the key challenges for cache compression: achieving *low decompression latency* (which is on the critical path of the execution) while maintaining *high compression ratio*. Our algorithm is based on the observation that many cache lines have data with a *low dynamic range*, and hence can be represented efficiently using base-delta encoding. We demonstrate the efficiency of the algorithm inspired by this observation (called *Base-Delta-Immediate Compression*) and the corresponding compressed cache design.

Second, we show that *compressed block size* is a new piece of information to be considered when making cache management decisions in a compressed (or even an uncompressed) cache. Including this new piece of information helps to outperform state-of-the-art cache management mechanisms. To this end, we introduce *Compression-Aware Management Policies* described in **Chapter 4**.

Third, we propose a new design for main memory compression, called *Linearly Compressed Pages* (**Chapter 5**). This mechanism solves a key challenge in realizing data compression in main memory – the disparity between how the data is stored (i.e. page granularity), and how it is accessed (i.e. cache line granularity).

Fourth, we show that bandwidth compression, both on-chip and off-chip, can be efficient in providing high effective bandwidth increase in the context of modern GPUs. Importantly, we discover that there is a new problem with bandwidth compression that makes compression potentially energy inefficient – number of *bit toggles* (i.e. the number of transitions between zeros and ones) increases significantly with compression, which leads to an increase in dynamic energy. This problem was completely overlooked by the prior work on bandwidth compression. We propose several potential solutions to this problem using our new *Energy Control* mechanisms (**Chapter 6**).

# Chapter 3

# **Base-Delta-Immediate Compression**

#### 3.1 Introduction

To mitigate the latency and bandwidth limitations of accessing main memory, modern microprocessors contain multi-level on-chip cache hierarchies. While caches have a number of design parameters and there is a large body of work on using cache hierarchies more effectively (e.g., [72, 96, 190, 194, 209, 211, 212, 192, 189, 107, 108, 235]), one key property of a cache that has a major impact on performance, die area, and power consumption is its *capacity*. The decision of how large to make a given cache involves tradeoffs: while larger caches often result in fewer cache misses, this potential benefit comes at the cost of a longer access latency and increased area and power consumption.

As we look toward the future with an increasing number of on-chip cores, the issue of providing sufficient capacity in shared L2 and L3 caches becomes increasingly challenging. Simply scaling cache capacities linearly with the number of cores may be a waste of both chip area and power. On the other hand, reducing the L2 and L3 cache sizes may result in excessive off-chip cache misses, which are especially costly in terms of latency and precious off-chip bandwidth.

One way to potentially achieve the performance benefits of larger cache capacity without suffering all disadvantages is to exploit *data compression* [10, 64, 73, 74, 256, 264]. Data compression has been successfully adopted in a number of different contexts in modern computer systems [83, 268] as a way to conserve storage capacity and/or data band-

Originally published as "Base-Delta-Immediate Compression: Practical Data Compression for On-Chip Caches"in the 21st International Conference on Parallel Architectures and Compilation Techniques, 2012 [185].

width (e.g., downloading compressed files over the Internet [214] or compressing main memory [3]). However, it has not been adopted by modern commodity microprocessors as a way to increase effective cache capacity. Why not?

The ideal cache compression technique would be *fast*, *simple*, and *effective* in saving storage space. Clearly, the resulting compression ratio should be large enough to provide a significant upside, and the hardware complexity of implementing the scheme should be low enough that its area and power overheads do not offset its benefits. Perhaps the biggest stumbling block to the adoption of cache compression in commercial microprocessors, however, is *decompression latency*. Unlike cache *compression*, which takes place in the background upon a cache fill (after the critical word is supplied), cache *decompression* is on the critical path of a *cache hit*, where minimizing latency is extremely important for performance. In fact, because L1 cache hit times are of utmost importance, we only consider compression of the L2 caches and beyond in this study (even though our algorithm could be applied to any cache).

Because the three goals of having *fast*, *simple*, and *effective* cache compression are at odds with each other (e.g., a very simple scheme may yield too small a compression ratio, or a scheme with a very high compression ratio may be too slow, etc.), the challenge is to find the right balance between these goals. Although several cache compression techniques have been proposed in the past [10, 38, 54, 73, 256], they suffer from either a small compression ratio [54, 256], high hardware complexity [73], or large decompression latency [10, 38, 73, 256]. To achieve significant compression ratios while minimizing hardware complexity and decompression latency, we propose a new cache compression technique called **Base-Delta-Immediate** ( $\mathbf{B}\Delta\mathbf{I}$ ) compression.

#### 3.1.1 Our Approach: $B\Delta I$ Compression

The key observation behind **Base-Delta-Immediate** ( $\mathbf{B}\Delta\mathbf{I}$ ) compression is that, for many cache lines, the data values stored within the line have a *low dynamic range*: i.e., the relative difference between values is small. In such cases, the cache line can be represented in a compact form using a common *base* value plus an array of relative differences ("*deltas*"), whose combined size is much smaller than the original cache line. (Hence the "*base*" and "*delta*" portions of our scheme's name).

We refer to the case with a single arbitrary base as Base+Delta (B+ $\Delta$ ) compression, and this is at the heart of all of our designs. To increase the likelihood of being able to compress a cache line, however, it is also possible to have *multiple bases*. In fact, our results show that for the workloads we studied, the best option is to have *two bases*, where